英特尔小芯片战略加速FPGA开发

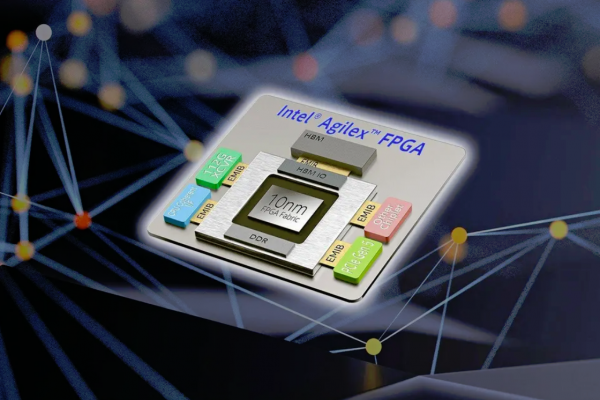

英特尔Agilex FPGA在封装中引入小芯片,用以添加接口功能和高带宽内存。

尽管小芯片似乎是近年来才开始在半导体领域大规模普及,但英特尔可编程解决方案部门(PSG)其实早在2016发布的首款Stratix 10设备以来,就一直依赖小芯片技术实现其现场可编程门阵列(FPGA)。这些FPGA采用英特尔的嵌入式多芯片互连桥(EMIB)封装技术,将主FPGA芯片与各种接口及内存小芯片对接起来。如今,英特尔采用相同的EMIB封装技术将小芯片集成至下一代英特尔Agilex FPGA当中。这种基于小芯片的设计方法具备一大显著优势,允许英特尔快速在其FPGA产品家族中引入新的成员,而这已然成为PSG部门所依靠的一大核心能力。从各个角度来看,这种快速推出家族新成员的能力,已经给英特尔的FPGA客户群体带来巨大好处。

小芯片封装使得英特尔PSG能够为其FPGA添加各种新功能,包括:

- 2018年2月:58 Gbps PAM4收发器;

- 2019年8月:PCIe 4.0支持能力;

- 2019年11月:业界首款具有超1000万个逻辑元件的FPGA;

- 2022年4月:PCIe 5.0 x16,运行速度可达320亿次传输/秒;

- 2022年9月:直接模拟/数字射频(RF)转换速度为640亿次转换/秒;

- 2023年3月:116 Gbps PAM4收发器;

- 2023年5月:支持PCIe 5.0与CXL硬件。

英特尔PSG总经理兼副总裁Deepali Trehan表示,英特尔FPGA中的小芯片功能是客户决定在其系统设计中选择这些FPGA产品的主要原因。在FPGA中使用小芯片,使得英特尔能够率先将上述先进功能引入产品,在保持技术领先的同时降低开发风险、并大大缩短开发时间。

作为英特尔FPGA的长期客户之一,BittWare公司负责开发基于外围组件互连Express(PCIe)总线标准的基于FPGA加速卡。BittWare过去20年间一直在基于英特尔FPGA开发PCIe加速卡产品。这些PCIe卡可用于计算加速、网络与传感器融合,并经常在边缘应用中配合英特尔至强CPU作为高性能数据处理器与输入/输出(I/O)引擎。

Molex BittWare业务部门总经理兼副总裁Craig Petrie指出,在FPGA中使用小芯片可以比其他方式更快为FPGA带来新的I/O功能。组件层面的快速发布能力,使得BittWare的板级产品也能获得同样敏捷的上市时间。Petrie还特别指出,小芯片使BittWare能够快速、连续推出带有PCIe 4.0、PCIe 5.0、Compute Express Link(CXL)和高速以太网端口的加速卡。

Petrie表示,“Tiles(小芯片)解决了一个重大问题。”就是说,如果需要为每种新的I/O标准(例如各代PCIe和以太网标准)设计新的单片FPGA,则不可避免要要在FPGA的整体设计上做出一些细微调整。BittWare需要针对这些微小变化做设计调整,而调整终归需要额外的设计时间。但通过小芯片来实现这些I/O功能,FPGA的核心部分(主芯片)可以继续维持不变。因此,小芯片允许英特尔等半导体厂商能够更快适应新的I/O功能,且无需重新设计主FPGA芯片。Petrie强调,“这样就降低了我们的设计风险。”

Liquid-Markets-Solutions (LMS)公司联合创始人、总裁兼CEO Seth Friedman对基于小芯片的FPGA也有类似的看法。这家公司开发了名为“ÜberNIC”的网络接口卡(NIC),最初专为金融市场的高速交易需求而生。在这部分市场中,每一微秒的变化都极其重要,速度较慢的交易在利润上根本无法与速度较快的交易相匹敌。为此,LMS开发出一套快速、基于硬件的完整以太网协议栈,并将其引入网卡上的英特尔FPGA当中,借此满足金融业客户对于低延迟的严苛要求。

但LMS很快发现,许多其他涉及电信、计算、广播、研究和学术界的组织也同样需要高速网卡,包括测试设备、建立自动视觉系统等。另外,云服务提供商和超大规模基础设施提供商的数据中心对于高速网卡也有着旺盛需求。

Friedman指出,FPGA中的小芯片通过PCIe 5.0端口为其带来了上市时间方面的优势,同时也让他们得以快速引入CXL 1.1和2.0。“这一切,都要归功于小芯片技术。”Friedman还解释道,小芯片对LMS有着另外一个重大优势:收发器密度。基于小芯片的FPGA能配备大量高速以太网收发器,帮助LMS将2到4倍数量的光纤接入同一款ÜberNIC网卡。

LMS选择英特尔FPGA的目的不只是看重其I/O优势。如前文所言,FPGA中的可编程硬件允许该公司构建高速以太网协议引擎,此外FPGA还保留了灵活空间,可用于整合对最终客户具有巨大价值的其他附加功能。例如,LMS已经将英特尔第四代至强Scalable CPU中的精密时间测量(PTM)功能引入其ÜberNIC网卡。PTM可以通过独立的本地时钟精确协调多个组件间的事件。这种精确的时间功能可在高速金融交易中创建准确的时间戳,同时也能为数据流提供精确的时间戳。这种能力借助的正是FPGA所提供的可编程硬件,“传统网卡则无法提供此项功能。”

BittWare和LMS等客户的赞许,也让英特尔坚定了在FPGA路线图中继续使用小芯片的决心。目前,英特尔PSG的FPGA依赖于EMIB封装技术和英特尔开发的所谓高级接口总线(AIB)协议。英特尔随后将其作为开源、免版税标准贡献给了CHIPS联盟。然而,如今英特尔PSG的发展路线图已经超越了目前EMIB和AIB的使用范围。

英特尔公司的Trehan表示,“UCIe对于我们的下一代FPGA来说极为重要。”他所指的,是目前由UCI Express开发的Universal Chiplet Interconnect Express (UCIe)标准。UCI Express是英特尔去年3月与Advanced Semiconductor Engineering(ASE)、AMD、Arm、Google Cloud、Meta、微软、高通、三星和台积电共同成立的行业联盟及非营利组织。通过将UCIe作为小芯片的互连标准,Trehan预计未来会诞生出小芯片市场,由各家代工厂使用不同的半导体制程工艺进行制造,再由英特尔组装出具备各种电子特性(包括氮化镓)并直接集成有高速光学I/O的FPGA封装。这些新功能,将为FPGA带来全新的应用前景。

目前,小芯片在高端半导体设备中的应用已经成熟,其后盾正是FPGA所开创的多年实践经验。小芯片如今开始在CPU和GPU中占据一席之地。研究机构TIRIAS Research认为,未来小芯片的应用将在这些高端设备中持续扩张,以添加新的特性/功能、提高性能并延长摩尔定律的寿命,同时满足客户对于上市时间的严苛要求。而由全行业联盟UCIe开发的小芯片间接口标准将进一步加快这种趋势。与此同时,单片结构则继续作为最便宜的封装方案选项,在低成本半导体器件的制造中维持长久以来的主导地位。

好文章,需要你的鼓励

谷歌免费存储空间调整:未绑定手机号仅享5GB

谷歌近期悄然调整账户存储政策:新注册用户若未绑定手机号,免费存储空间将从原来的15GB缩减至5GB。用户需验证手机号后,方可获得完整的15GB空间,用于Gmail、Drive和Photos的共享使用。谷歌表示,此举旨在确保存储空间"每人仅限一份",有效防止滥用。有分析认为,存储硬件成本上升也是推动此次政策调整的重要原因之一。

AI助手越权了?南加州大学等机构揭示大模型代理的“权限失控“问题

FORTIS是专门测量AI代理"越权行为"的基准测试,研究发现十款顶尖模型普遍选择远超任务需要的高权限技能,端到端成功率最高仅14.3%。

美国三大运营商携手卫星技术,向信号盲区宣战

AT&T、Verizon和T-Mobile宣布计划组建合资企业,利用卫星技术消除美国境内的网络覆盖盲区,重点服务农村及网络欠发达地区。该合资企业将整合知识产权与地面频谱资源,推动下一代直连设备(D2D)通信发展。目前三方尚未签署正式协议,现有运营商与卫星服务协议不受影响。此前,T-Mobile已与SpaceX合作推出星链卫星服务,美国联邦通信委员会也刚批准了价值400亿美元的EchoStar频谱出售案。

荷兰Nebius团队:给AI“起草员“瘦身,大模型推理速度最高提升5倍的秘密

荷兰Nebius团队提出SlimSpec,通过低秩分解压缩草稿模型LM-Head的内部表示而非裁剪词汇,在保留完整词汇表的同时将LM-Head计算时间压缩至原来的五分之一,端到端推理速度超越现有方法最高达9%。

美国三大运营商携手卫星技术,向信号盲区宣战

Flytrex无人机携手达美乐,可一次性送达两个大号披萨

欧洲最大3D打印公寓楼提前数月竣工

彼亚乔携手迪士尼推出Grogu主题自主跟随货运机器人

Okta将AI智能体安全管理扩展至Amazon Bedrock并向第三方身份提供商开放

苹果13英寸iPad Pro Magic键盘键盘亚马逊历史低价,直降25%

WhatsApp iOS版Liquid Glass界面设计正式向更多用户推送

OpenAI为ChatGPT Pro推出个人财务管理新功能

赛格威全新Xaber 300电动越野摩托车正式开售,最高时速达96公里

OpenAI再度重组高管架构,全力押注AI智能体战场

出门在外也能用!OpenAI 将 Codex 接入 ChatGPT 移动端

Google Gemini应用图标迎来细微配色调整