AI覆盖EDA全流程,开启一场“双向奔赴”的变革 原创

近年来,5G、自动驾驶、超大规模计算和工业物联网产业发展势头强劲,这些产业的背后是AI(人工智能)和ML(机器学习)的大规模应用。毋庸置疑,新的应用和技术相辅相成,并催生出更复杂计算、更强功能、更快数据传输速度的需求。这对芯片工作者而言是一个新开发者带来了全新且复杂的挑战——下一代芯片的开发必须更快、更智能。

AI + EDA 开启芯片设计新“智”元

当前,算力与储存需求爆发式增长,先进SoC的设计、验证压力呈指数级增长,开发者所需要的工具早已不局限在满足功能验证需求,而是需要从设计、架构、软硬协同、功耗等方面协同优化。

对于芯片制造企业而言,为保持竞争优势,不断缩减上市时间,这对流片的成功率也提出了更高的要求。一旦流片失败,将会给造成企业重大损失。2023年,Wilson Research Group 发布的一份芯片验证调研报告显示,芯片制造企业首次流片的成功率正在下降,只有24%,这也意味着企业正面临着越来越昂贵的重新设计成本及不断增加的上市时间。

作为芯片设计领域的“基座技术”,EDA的全流程创新将撬动芯片产业的巨大变革。

那么,EDA变革的方向在哪里?如果说EDA工具飞速演进的触发点之一是为适应飞速攀升的AI算力,那么“AI+EDA”便是开启了一场“双向奔赴”的“良性循环”。

2023年伊始,机器学习(ML)和人工智能(AI)开始向几乎每一个领域进军。半年过去,AI带来的算力风暴仍在扩散。随着对AI应用可能性的不断挖掘,AI+EDA这一概念火速在业界获得认可。业内认为,AI赋能EDA将重塑芯片产业格局。

AI+EDA可以帮助芯片拓宽摩尔定律的边界,节约时间和资金成本,缓解人才短缺困境,甚至推动芯片设计迈入新“智”元。

目前,学术界、产业界都已注意到AI给EDA产业带来巨大的变革驱动力。德勤预计,2023年全球半导体企业将投入3亿美元,利用内部自有或第三方AI工具开展芯片设计,且未来四年这一数字将每年增长20%,到2026年将超过5亿美元。2023年先进AI芯片设计工具业务将迅速增长,预计其增长率将超过EDA工具业务增速的两倍以上,且超过芯片销售增速的三倍以上。

如今,AI在EDA领域的应用已经有了实质性进展。EDA和半导体IP的全球领导者新思科技(Synopsys)很早便敏锐地察觉到,利用AI技术优化芯片设计流程,能够极大地助力芯片设计降本增效。2020年,新思科技推出了全球首个AI自主芯片设计解决方案DSO.ai (Design Space Optimization AI),开启了一场AI与EDA的“双向奔赴”。

DSO.ai完成超进化,Synopsys.ai引发行业颠覆性变革

2020年初,新思科技推出的DSO.ai,掀起芯片设计领域的新一轮革命。作为业界首个用于芯片设计的自主人工智能(AI)应用,DSO.ai能够在巨大的芯片设计解决方案空间中搜索优化目标,利用强化学习来优化功耗、性能和面积。

当前,DSO.ai已经完成了超过200次商业生产流片。这个重要的里程碑,标志着AI在芯片设计中的规模化应用实现了新突破,“AI+EDA”已经成为主流的半导体技术之一。

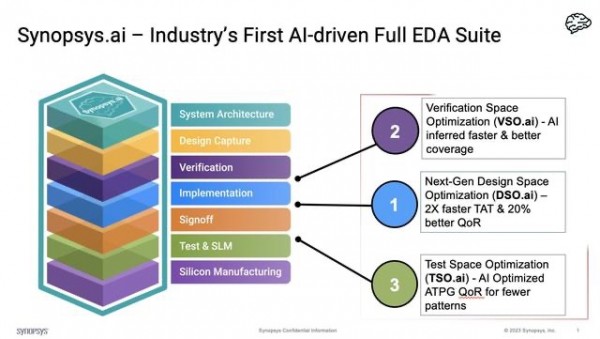

基于DSO.ai的成功,新思科技的AI研发团队很快着眼于将AI深入到芯片设计的其他领域,研究能否利用AI技术进一步提高设计结果质量(QoR)和生产力。2023年4月,新思科技Synopsys.ai全栈式AI驱动型EDA解决方案应运而生,涵盖了设计、验证、测试和模拟电路设计阶段,让开发者第一次从系统架构到设计和制造、在芯片开发的每一个阶段都可以采用AI技术,并从云端访问这些解决方案,最终达到降本增效,并缩短产品开发周期的优异成果。

如果说DSO.ai引领着AI设计芯片进入规模化时代,那么Synopsys.ai便是基于实现更好、更快、更普惠的半导体愿景而创新出来的颠覆性产品。

Synopsys.ai解决方案可提供诸多AI驱动的解决方案,包括:数字化设计空间优化以实现功耗、性能和面积(PPA)目标,并提高生产效率;模拟设计自动化,实现模拟设计跨工艺节点的快速迁移;验证覆盖率收敛和回归分析,以实现更快的功能测试收敛、更高的覆盖率和预测性错误检测;自动测试生成,可减少并优化测试模式,提高芯片缺陷覆盖率并加快获取测试结果;制造解决方案,可加速开发高精度光刻模型,以大幅提高芯片良率。

据新思科技介绍,完整的Synopsys.ai解决方案将覆盖先进数字与模拟芯片的设计、验证、测试和制造环节,现已搭载物理实现解决方案(DSO.ai)、功能验证解决方案(VSO.ai)和芯片测试解决方案(TSO.ai),未来还将推出更多功能,并针对模拟电路设计进行优化,目标到2024年覆盖全流程,最终让IC设计每阶段都能用上AI不是梦。

VSO.ai治好了流片前的“拖延症”

在IC设计的全流程中,芯片验证是芯片设计企业最重视的流程之一。

芯片验证不足造成的反复投片问题,是芯片企业的“心腹大患”。面对高昂的流片成本,可能导致芯片设计企业“血本无归”。这其中,造成芯片重复投片的主要原因之一就是验证不够充分。

芯片验证是一项颇具挑战性的工作,通常需要工程师团队编写代码,之后在EDA工具的辅助下完成电路设计。而随着芯片所承载的功能日益提高,验证需要探索的空间和范围越来越大,每一次验证都像是一次“大海捞针”,验证所需要的时间也因此越来越长。

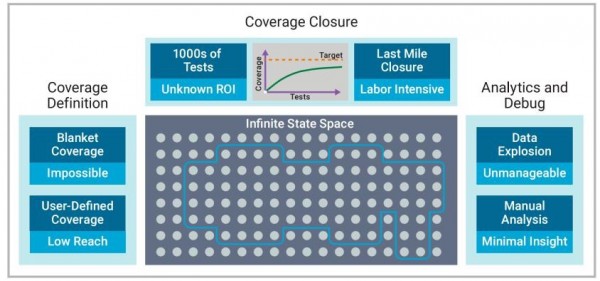

验证覆盖率是衡量验证效果的重要指标之一。然而,覆盖率却并没有具体的指标,这便为验证工程师增加了大量的重复性工作,因此手动进行回归优化的效率非常低,需要对给定设计进行上万次的测试。同时,传统工作流中功能覆盖率主要依赖验证开发者的经验,导致很多时候覆盖率收敛的效果较差。此外,由于验证工程师对已获取的验证大数据所具有的洞察力和分析能力的局限性,过往验证工程师的手动调整在验证的最后阶段,覆盖率收敛和ROI有限。

仿真验证中的覆盖率挑战

在验证工程师的经验成为芯片验证的明显瓶颈时,AI成为了一个新的解题思路。机器学习(ML)作为AI领域的颠覆性技术,能够在迭代循环中不断成长,并基于大数据发现代码中难以察觉的错误,进而实现更快速、更高质量的覆盖率收敛。

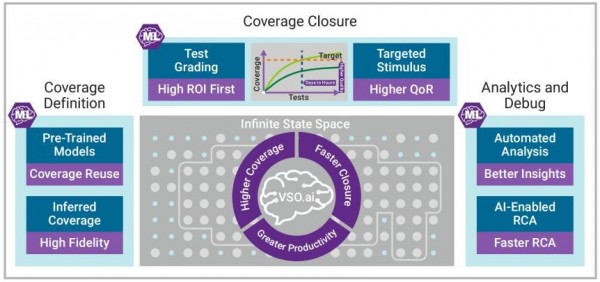

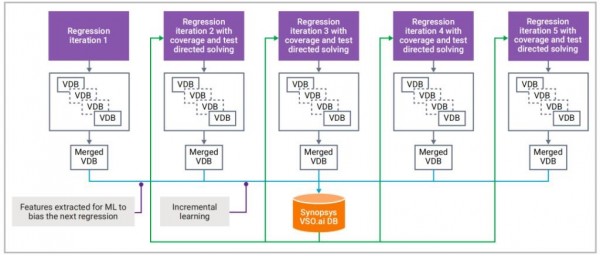

面对芯片企业“苦验证久矣”的困局,新思科技推出了全新一代VCS工具中用于覆盖率提升的技术VSO.ai,也是Synopsys.ai中搭载的重要工具之一。VSO.ai是一套自主工作系统,用以替代验证工程师负责的编译设计和编排测试等工作,以尽可能快、尽可能低开销地达到覆盖率目标,并获得最高质量的验证结果。

VSO.ai对仿真覆盖率的改进

VSO.ai能够从三个方面给验证工程师带来非凡的助力:

1、实现更快的覆盖率收敛。VSO.ai可执行粗粒度基准测试,提供自动化的、自适应的测试优化。在运行过程中,VSO.ai会率先运行具有最高ROI的测试,同时消除冗余测试,从而加速覆盖收敛并节省计算资源。

2、实现更高的测试质量。VSO.ai可执行细粒度的基准测试,通过调整随机约束激励来针对未被验证的覆盖点,自动发现测试覆盖率中难以捉摸的错误,进而提升测试质量。

3、攻克“最后一公里”的验证难题。VSO.ai可执行根本原因分析(RCA),以确定没有达到特定的覆盖点的原因,并通过AI解决最后的难题。

在整个仿真测试流程中,面对验证工程师对于覆盖率有差异化需求,VSO.ai能够提供新的信息来改进约束求解和优化回归测试,以便于验证工程师可以灵活设置覆盖率目标。

VSO.ai使用ML改进回归分析

不仅如此,VSO.ai还具备可集成特性,可以轻松集成到现有的新思科技VCS回归环境中,无需对设计或测试平台进行任何代码更改。

新思科技表示,Synopsys.ai已经在减少功能覆盖率漏洞方面实现10倍提升,IP验证效率提高30%。据了解,瑞萨电子借助新思科技 VCS功能验证解决方案进行AI驱动的验证,在减少功能覆盖率漏洞方面实现了10倍以上的提升,同时IP验证效率提高了30%。

生产力Up Up Up,能耗也要Down Down Down

尽管AI已经实现了覆盖EDA全流程,大幅提升了芯片设计的生产力,但其所需的强大算力背后,是能源消耗的问题。

这方面,新思科技也早有布局。通过利用新思科技从架构到签核的整体性软件驱动方法,开发者能够在提升效率的同时,降低能耗。

软件方面,在SoC设计过程中,软件的作用包括协调芯片中的电源管理,以及确定功耗分析和优化的关键场景。因此,有必要通过分析和优化软件来确保SoC实现最佳能效。

架构方面,动态电压频率调整(DVFS)、电源域和电压岛等电源管理策略可以带来显著的节能效果。除了这些策略外,功耗与性能的宏架构权衡,以及IP选择和权衡,可以节省30%至50%的电能。

RTL(寄存器传输级)方面,时钟、数据、内存和毛刺(自激震荡)功耗的微架构权衡有助于实现节能,查找和修复RTL电源块以及使用工具引导的时钟门控、数据门控和内存大小调整也是如此。在这方面可能实现的节能效果将达到15%至30%。

实现效果方面,在动态和泄漏功耗、电源完整性与功耗、性能和面积(PPA)权衡,以及功耗感知测试码生成等领域采用自动优化技术,可实现10%至15%的节能效果。

签核方面,通过采用以签核为中心的方法实现功耗和电源完整性目标,再加上动态和泄露功耗回收以及非常精确的工程变更命令(ECO)更改,可实现5%至10%的节能效果。

验证方面,通过将验证工作集中在UPF功耗设计意图验证和UPF驱动的功能验证,有助于提高能效。

据了解,利用新思科技从架构到签核的整体性软件驱动方法,能够帮助开发者们实现50%的能效提升。

如今,新思科技已经将目光从上游出发,拓展到全行业,探索如何将芯片设计中的能耗技术和思路迁移到传统能源领域,直接投入到低碳化事业当中。

面对人才短缺,采“远水” 也解“近渴”

除了能耗问题,新思科技也长期关注并致力于改善芯片领域的人才短缺困局。

根据中半协数据预测,到2024年半导体行业人才总规模将达到79万左右,而人才缺口将达到23万人左右。

面对当下的“燃眉之急”,AI与EDA工具结合衍生出的Synopsys.ai,恰恰能帮助开发者减少重复且繁杂的工作,让他们专注于最重要的创芯工作。得益于AI的自主学习能力,AI赋能的EDA工具将大幅降低使用者的门槛,助力半导体行业应对人才短缺挑战。

新思科技介绍,这种高度自动化的工具大幅提高了设计效率,大幅缩短设计周期,帮助开发者能够在更短的时间内完成芯片设计。比如,借助DSO.ai,一个只有几年工作经验的开发者,也能达到有多年丰富经验开发者的设计水准。此外,DSO.ai还能够在庞大的芯片设计空间中搜索优化目标,帮助开发者更快地找到最佳解决方案。

然而,新思科技深知,不断提高现有生产力是一方面,为行业培养下一代人才才是“硬道理”。

近年来,新思科技也拓宽了人才培养的步伐。2023年,新思科技创新性地讲芯片相关的知识与初高中生的数理化教育结合起来,通过科普教育更早启蒙青少年对于芯片创新的认知和探索,从而确保创新人才的可持续性。

写在最后

如今,AI与EDA工具的结合已进入了一个全新的阶段,随着训练数据量的不断攀升,数据精度不断提高,EDA工具性能也将进一步提升。放眼未来,随着新思科技等一众领军企业的技术革新,AI+EDA模式或将在复杂的芯片甚至系统级创新的架构中发挥重要作用。

对于行业而言,则需要建立“AI+EDA”的生态,开拓人才生态圈,制定相应的规范,以确保AI辅助EDA健康发展。

好文章,需要你的鼓励

AGI-Next峰会全记录解读:Kimi、Qwen、智谱、腾讯同台,2026年有新范式是共识,中国引领AI概率最低预测2成

中国AI的一个挑战是:美国算力规模大1-2个数量级,且大量投入下一代Research,中国公司光交付就占据了绝大部分资源。

上海AI实验室让机器人“睁眼看世界“:用视觉身份提示技术让机械臂学会多角度观察

上海AI实验室联合团队开发RoboVIP系统,通过视觉身份提示技术解决机器人训练数据稀缺问题。该系统能生成多视角、时间连贯的机器人操作视频,利用夹爪状态信号精确识别交互物体,构建百万级视觉身份数据库。实验显示,RoboVIP显著提升机器人在复杂环境中的操作成功率,为机器人智能化发展提供重要技术突破。

Anthropic推出医疗健康功能助力患者理解病历记录

人工智能开发商Anthropic为其旗舰聊天机器人Claude推出新的医疗健康功能,用户现在可以与服务共享医疗记录以更好地了解自己的健康状况。Claude可以连接官方医疗记录和苹果健康等健身应用,进行更个性化的健康对话。新功能现已向美国的Claude Pro和Max订阅用户开放。公司强调该工具不用于诊断或治疗建议,而是帮助用户理解复杂医疗报告,为医患沟通做准备,并承诺严格保护用户隐私数据。

英伟达团队突破AI训练瓶颈:让机器人同时学会多种技能不再“顾此失彼“

英伟达研究团队提出GDPO方法,解决AI多目标训练中的"奖励信号坍缩"问题。该方法通过分别评估各技能再综合考量,避免了传统GRPO方法简单相加导致的信息丢失。在工具调用、数学推理、代码编程三大场景测试中,GDPO均显著优于传统方法,准确率提升最高达6.3%,且训练过程更稳定。该技术已开源并支持主流AI框架。

iOS 18新增游戏应用正式上线,专为iPhone游戏体验而生

CES 2026推出AI伴侣机器人Emily

苹果2026年将发布四款新iPhone机型预览

AGI-Next峰会全记录解读:Kimi、Qwen、智谱、腾讯同台,2026年有新范式是共识,中国引领AI概率最低预测2成

Anthropic推出医疗健康功能助力患者理解病历记录

Google推出通用商务协议,推动智能体购物自动化

核电初创公司携小型反应堆回归,面临重大挑战

谷歌针对部分医疗查询移除AI概览功能

Motional采用AI优先策略重启无人驾驶出租车计划

新年存储升级:三星SSD优惠最高减免100美元

OpenAI与软银联手投资10亿美元,助力星门项目能源伙伴发展

Uber联合Lucid和Nuro发布全新自动驾驶出租车