英特尔Agilex 7 FPGA R-Tile现已量产,为CPU提供行业领先的带宽

在技术创新的推动下,从边缘计算到云的新连接和处理模型也在高速发展,随之而来的,则是对灵活硬件解决方案与日俱增的需求。随着市场上对带宽的要求不断增加,对更快、更灵活的设备的需求也日益迫切。而于近期推出的英特尔Agilex® 7 FPGA R-Tile,凭借其高带宽接口和灵活的可编程逻辑,能够满足行业发展需求。目前,基于R-Tile的英特尔Agilex 7 FPGA正在量产。

近年来,FPGA 加速器在市场上的应用率稳步增长,而随着配备R-Tile的FPGA 的推出,更高性能的加速器也随之而来。FPGA 加速器可以将任务从主机CPU 卸载,释放CPU核心并减少总功耗,实现总拥有成本(TCO)的节省。如您作为最终用户、IT专家或云服务提供商,且尚未探索使用FPGA加速器,现在则是一个良好的尝试时机。

- 使用FPGA加速器的云服务提供商可以支持更多用户,并释放更多CPU核心给更多的用户,从而获得更多服务收入。

- 利用FPGA加速器的原始设备制造商可以节省成本并减少功耗。

英特尔Agilex® 7 FPGA产品系列已应需设计以满足市场要求,而且基于R-Tile的版本已经开始量产。

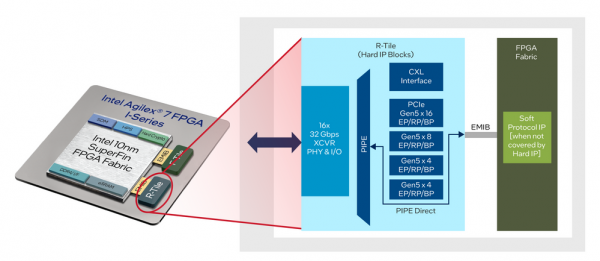

英特尔Agilex® 7 FPGA采用了异构多芯片架构,其中位于中心位置的FPGA芯片与收发器芯粒通过英特尔的嵌入式多芯片互连桥接(EMIB)封装技术相连。每个芯粒或区块都是一个小型集成电路芯片,包含一组明确定义的硬化功能子集。这些芯粒使得成本高效的,封装内部高密度互连异构芯片成为现实。通过采用异构多芯片架构和芯粒的设计,英特尔能够在单个设备中提供多样化的功能和灵活性,以满足不同应用的需求。这种方法消除了使用多个设备进行连接的需要,简化了系统设计和集成的复杂性,并提供了更高的可扩展性和性能。

诸多英特尔Agilex® 7 FPGA封装组合中都包含了R-Tile芯粒,旨在与高性能CPU 连接时可提供行业领先的带宽。R-Tile芯粒结合了PCIe 5.0 x16和CXL 1.1/2.0 的硬化知识产权(IP)块和软件IP代码,为网络、云计算、数据中心、科学计算等诸多领域提供了高度灵活的解决方案。如下是R-Tile支持的关键技术特性列表:

图1. 英特尔Agilex® 7 FPGA与R-Tile模块的图解

|

R-Tile特性(每个区块) |

描述 |

|

PCle 5.0 x16 Up to32GT/sper lane 1x16EP/RP 2x8EP/RP 4 x4 RP 端点(EP)Root Port(RP)PIPE直接事务层旁路/切换选项 虚拟化&确切时间选项 |

灵活的、多功能的PCIe 5.0硬化IP模块,允许您在高性能FPGA设计中创建端点、根端口、交换机或定制的PCIe接口。 Intel Agilex 7 FPGA R-Tile是唯一具备完整的50x16数据速率且符合PCI-SIG标准的设备。 |

|

CXL1.1/2.0x16 Up to 32 GT/s per lane 1x16 EP Supports CXL Type1 Type2 with DCOH and Type 3. |

这是FPGA行业中首款具有CXL硬化IP的设备,可以以全速率管理链接并预处理CXL数据包。软件协议IP管理CXL事务层功能。图形用户界面(GUI)允许进行以下自定义操作:

与第四代英特尔® 至强® 可扩展处理器进行了广泛的验证和互操作性测试。CXL认证待定,将在Compute Express Link协会的活动中进行。 预计支持选定的CXL 2.0功能,待验证、互操作性测试和与未来CPU的合格性确认后提供支持。 |

表1. 英特尔Agilex® 7 FPGA R-Tile关键特性

符合量产要求的R-Tile版本标志着英特尔Agilex® 7 FPGA I系列设备中四种不同封装下的七种逻辑密度的器件进入量产阶段。这样一来,客户就能够在他们的新设计中充分利用英特尔Agilex® 7 FPGA提供的性能和功耗领先优势。基于英特尔10纳米工艺技术,英特尔Agilex® 7 FPGA可编程逻辑和R-Tile芯粒充分利用英特尔强大的供应链优势,以及先进的制造和测试能力,能够在标准交货期内提供量产解决方案。一旦英特尔Agilex® 7 FPGA M系列R-Tile的样品过渡到量产阶段,将具备更多设备密度和封装选项。

将R-Tile的功能与其他的英特尔Agilex® 7 FPGA芯粒(如最近发布的F-Tile)相结合,可以创建出适用于下一代加速器(如SmartNIC、IPU和计算存储解决方案)的灵活高性能FPGA。

来源:业界供稿

好文章,需要你的鼓励

苹果48GB M5 Pro MacBook Pro创历史新低,直降300美元

B&H近期对多款M5 Pro MacBook Pro机型推出300美元优惠。14英寸M5 Pro版本(48GB内存+1TB固态硬盘)现售价2299美元,较原价2599美元节省300美元,且该配置在亚马逊无法购买,折扣机会更为难得。此外,16英寸M5 Pro版本(64GB内存+1TB固态硬盘)同样享有300美元折扣。B&H在多款高配MacBook机型上的定价已低于亚马逊,是近期可找到的最优价格。

AI助手越权了?南加州大学等机构揭示大模型代理的“权限失控“问题

FORTIS是专门测量AI代理"越权行为"的基准测试,研究发现十款顶尖模型普遍选择远超任务需要的高权限技能,端到端成功率最高仅14.3%。

Insta360 GO 3S复古套装:怀旧美学与4K影像的融合

Insta360推出GO 3S复古套装,将现代4K运动相机与胶片时代美学结合。套装核心仍是仅重39克的GO 3S,新增复古取景器、胶片风格滤镜、NFC定制外壳及可延长录制时长至76分钟的电池组。复古取景器模仿老式腰平相机设计,鼓励用户放慢节奏、专注构图。相机内置11种色彩预设及负片、正片等滤镜,同时保留FlowState防抖、4K拍摄及10米防水能力,面向热衷复古影像风格的年轻创作者。

荷兰Nebius团队:给AI“起草员“瘦身,大模型推理速度最高提升5倍的秘密

荷兰Nebius团队提出SlimSpec,通过低秩分解压缩草稿模型LM-Head的内部表示而非裁剪词汇,在保留完整词汇表的同时将LM-Head计算时间压缩至原来的五分之一,端到端推理速度超越现有方法最高达9%。

CarPlay 新增两款音频应用,让你的旅途更精彩

Insta360 GO 3S复古套装:怀旧美学与4K影像的融合

谷歌免费存储空间调整:未绑定手机号仅享5GB

美国三大运营商携手卫星技术,向信号盲区宣战

Flytrex无人机携手达美乐,可一次性送达两个大号披萨

欧洲最大3D打印公寓楼提前数月竣工

彼亚乔携手迪士尼推出Grogu主题自主跟随货运机器人

Okta将AI智能体安全管理扩展至Amazon Bedrock并向第三方身份提供商开放

苹果13英寸iPad Pro Magic键盘键盘亚马逊历史低价,直降25%

WhatsApp iOS版Liquid Glass界面设计正式向更多用户推送

OpenAI为ChatGPT Pro推出个人财务管理新功能

赛格威全新Xaber 300电动越野摩托车正式开售,最高时速达96公里