高通公司将骁龙芯片设计人员调往ARM服务器芯片部门 原创

本周Centriq 2400设计蓝图将正式发布。

高通公司数据中心芯片部门负责人Anand Chandrasekher手持Centriq芯片

高通公司曾将来自其旗舰级骁龙芯片(被数以百万计智能手机与平板设备所使用)开发团队的工程师们调往其刚刚起步的数据中心处理器Centriq芯片部门。

这种关注重点的转化意味着高通公司开始将注意力集中在服务器领域,而就在今天(星期二)晚,相关成果终将亮相——Centriq内部设计方案将在本届于硅谷召开的Hot Chips大会上公开。

将众多原本隶属骁龙部门的工程师重新调往Centriq可能恰好解释了为何高通公司决定将内部设计的移动Kryo核心替换为现成ARM Cortex核心——或者是经过轻微调整的版本。事实上,高通公司已经停止了全面定制化Kryo芯片的开发工作。

当然,仍有一部分移动CPU设计师继续留在骁龙研发团队当中,而且工程师们亦可根据需求随时被调回。根据我们掌握的情况,目前移动开发组仍然拥有充足的人手,能够继续推动骁龙芯片家族的顺利发展。这部分消息已经得到了高通公司多位高管的证实。

去年年末,高通公司发布了骁龙835,这款高性能系统级芯片将从今年开始由顶级Android智能手机过渡到Windows 10笔记本当中。这款处理器并未采用内部开发的Kryo核心,而是选择了经过轻松调整的现成CPU计算核心——很可能是四Coretex-A53加四A72或者A73的组合,且由ARM公司提供授权。高通方面将其称为“半定制”与“构建在ARM Cortex技术之上”的方案。

今年5月,高通公司面向智能手机发布了更为高端的骁龙处理器:660与630。然而,其中660采用了来自骁经820系列的八个Kryo核心,而630则采用八个ARM Cortex-A53核心。

这并不是说ARM公司的现成核心就不好。只是这种转变意味着高通公司的其它设计方案——包括其GPU、DSP、机器学习功能以及调制解调器——必须得想办法让其移动系统芯片焕发出独特的光彩,从而在与其它同样采用现成Cortex核心的厂商当中脱颖而出。这对于高通公司无疑是重要的一步,特别是考虑到其核心业务正是移动处理器与无线调制解调器芯片组。

值得一提的是,高通公司管理层表示,他们的想法是在正确的时间在移动端采用正确的计算核心——这意味着现成Cortex CPU在表现上显然优于高通内部设计的骁龙CPU。

转向数据中心领域

本周二晚上,Centriq 2400设计蓝图将由高通公司高层人士在本届于加利福尼亚州库比蒂诺召开的Hot Chips大会上向芯片工程师与计算机科学家们展示。我们此前曾经介绍过这款采用10纳米制程的ARMv8处理器产品线。高通公司曾在本周强调称,尽管设计人员来自骁龙处理器团队,但Centriq从设计之初就专门面向云计算与服务器工作负载等场景。

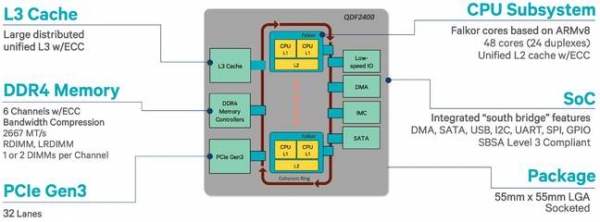

Centriq原理图

在这方面,很多朋友可能会对高通公司食言而肥的作法有所抱怨。在我们于上周看到的Hot Chips演示文稿当中,该公司表示Centriq处理器采用“第五代定制化核心设计”,旨在“从根本上满足云服务供应商的实际需求”。

Centriq产品管理高级主管Chris Bergen解释称,这意味着现有工程师团队,包括来自骁龙处理器开发组的成员,正在努力进行其第五代定制化CPU设计,且将从零开始打造出一款服务器友好型系统芯片。

然而着眼于蓝图本身,可以肯定的是这绝不是一款加大版的智能手机CPU。

这款代号为Falkor的处理器拥有48个计算核心,且仅能运行64位ARMv8代码。其并不提供32位模式。这款系统芯片支持ARM的虚拟机管理程序权限等级(简称EL2),可提供一套TrustZone(EL3)环境,且以可选方式包含AES、SHA1以及SHA2-256等加密算法的硬件加速能力。各计算核心被部署在一条环状总线之上,类似于英特尔刚刚停止在其至强处理器上使用的设计思路。芯片巨头并不喜欢以环状结构提升其芯片内的计算核心数量,转而选择了网状栅极——但高通方面则明显更喜欢这种快速双向频段思路。

其共享三级缓存被附加在环状结构当中,且看起来均匀分布在各计算核心之间。根据我们得到的消息,该环状互连结构的总传输带宽至少可达每秒250 GB。另外,据称这一环状结构还进行了分段,我们认为这代表着其中可能包含复数个环。因此,总计48个计算核心当中可能有24个处于一套环内,而另外24个核心则处于另一套环中,并由各环状体系将其对接在一起。

说到高速缓存,高通公司今年之内应该会实现这款芯片的量产,但并不会对缓存大小进行提升。每个计算核心拥有一个24 KB的64字节行零级指令缓存,一个64 KB 64字节行一级I-缓存,外加32KB一级数据缓存。其余的二级与三级缓存大小目前仍不明确。这款芯片目前仅提供样品,因此大家只能立足主流服务器芯片制造商英特尔公司的现有设计方案进行研究。高通公司显然不希望过早披露关键信息导致英特尔方面有所防备。

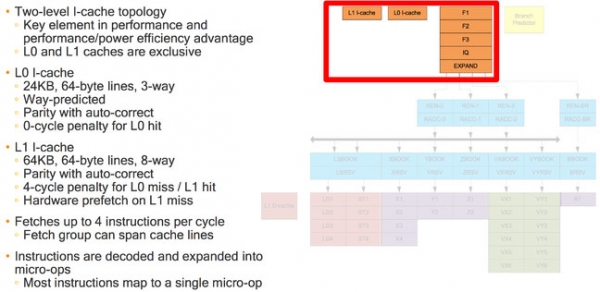

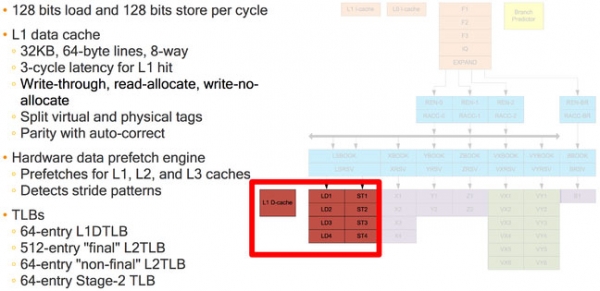

一级与零级缓存

其中零级缓存尤其值得关注:其作为一级I-缓存的扩展充当指令获取缓冲区。换句话来说,其很像是那种典型的前端缓冲区,每个周期会消耗四条指令,但具体作用则与缓存完全相同:例如,CPU可对其进行无效化与刷新。二级缓存则负责容纳数据与指令,且可实现128字节行八路运行,一次命中的最低延迟为15个周期。

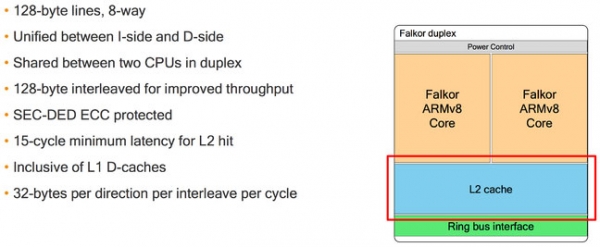

二级缓存

三级缓存拥有一项服务质量功能,允许各虚拟机管理程序与内核对虚拟机以及线程进行组织,以便确保拥有较高优先级的虚拟机能够占用较其它虚拟机更高的缓存容量。该芯片亦可实现实时内存压缩,延迟为2到4个周期,且面向软件开放。根据我们得到的消息,128字节行可被压缩为64字节行,并在可能的情况下进行纠错。

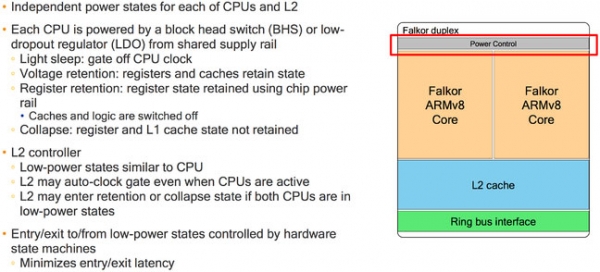

当高通公司提到48个计算核心时,最终产品一定就是48个计算核心——不存在任何超线程或者其它类似的缩水作法。Falkor芯片可对共享的二级缓存进行配对以实现双工传输。每个计算核心皆可开启与关闭,具体取决于工作负载需求——相当于由轻度睡眠(CPU时钟关闭)到全速运转。其提供32条PCIe通道,6条DDR4内存通道并配合有纠错功能。每通道拥有1到2个DIMM,外加SATA、USB、串行与通用IO接口。

功耗控制

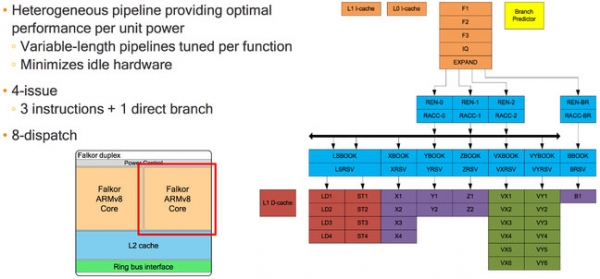

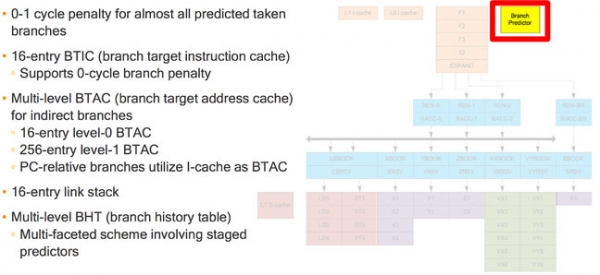

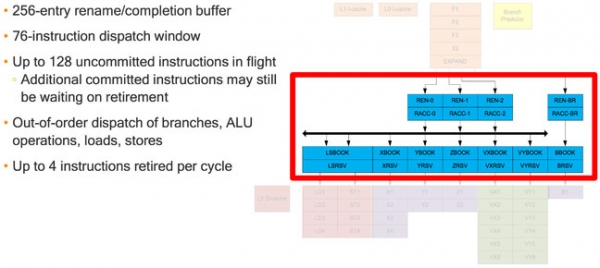

更进一步挖掘,可以发现其拥有可变长度管道,意味着可在每周期内最多发出三条指令外加一条直接分支。另外,其还拥有8条调度通道。其可实现无序执行,并对资源进行重命名。每个预测分支拥有一个0或1惩罚评分,一套16入口分支目标指令缓存,外加一套三级分支目标地址缓存。

Centriq的管道结构

分支预测器

管道队列

管道的负载存储分段

可变长度整数处理部分

这款芯片搭载有不可变片上ROM,其中包含一款启动加载程序,可用于验证通常被保存在闪存内的外部固件,同时确保仅运行合法代码。处理器内的安全控制器可容纳来自主通、服务器制造商以及客户的软件验证用加密公钥。因此,设备将仅在未从ROM或者早期启动加载程序中发现漏洞的前提下启动可信代码并构建信息来源。

在本周召开的Hot Chips大会上,我们将持续为大家带来更多新鲜出炉的重要消息。另外,当相关价格、缓存大小与其它信息得到披露之后,我们还将发文将至强、Centriq与Epyc进行一番规格比较。

好文章,需要你的鼓励

瑞典银行与政府联手加强国家网络安全防护体系

瑞典央行与金融机构及国家安全部门深化合作,共同应对网络威胁。今年5月,瑞典遭遇大规模分布式拒绝服务攻击,政府和金融机构受到严重冲击。总理克里斯特松承诺增加资金支持,建立更强大的公私合作伙伴关系。央行将举办第二届在线网络安全挑战峰会,鼓励金融机构提升网络安全能力。瑞典金融协会敦促建立危机管理机制,与国家网络安全中心等机构协调配合。

ByteDance推出Seedream 4.0:AI图像生成的新纪元,一秒生成4K图片的超级引擎

字节跳动发布Seedream 4.0多模态图像生成系统,实现超10倍速度提升,1.4秒可生成2K高清图片。该系统采用创新的扩散变换器架构,统一支持文字生成图像、图像编辑和多图合成功能,在两大国际竞技场排行榜均获第一名,支持4K分辨率输出,已集成至豆包、剪映等平台,为内容创作带来革命性突破。

5个强大ChatGPT指令快速减轻工作压力

工作压力源于大脑储存混乱而非系统。本文介绍5个ChatGPT提示词,帮你将工作压力转化为结构化行动:优先级排序任务清单、快速撰写专业邮件回复、从冗长文档中提取关键信息、生成问题解决方案、高效准备会议内容。通过系统化处理工作事务,将分散的精力转为专注执行,让大脑专注于决策而非重复劳动。

AI系统透明度新突破:红帽团队提出智能安全卡让AI系统更可信

红帽公司研究团队提出危险感知系统卡(HASC)框架,为AI系统建立类似"体检报告"的透明度文档,记录安全风险、防护措施和问题修复历史。同时引入ASH识别码系统,为AI安全问题建立统一标识。该框架支持自动生成和持续更新,与ISO/IEC 42001标准兼容,旨在平衡透明度与商业竞争,建立更可信的AI生态系统,推动行业协作和标准化。

IDC报告,深信服在2025年上半年位居中国超融合市场、中国全栈超融合市场第一

PTC 推出全新服务全生命周期管理 AI 解决方案,助力现场服务和服务供应链现代化

瑞典银行与政府联手加强国家网络安全防护体系

5个强大ChatGPT指令快速减轻工作压力

英伟达DGX Spark:小巧超算处理大模型的新选择

美中AI竞争升级:美国巨额交易对战中国开源策略

微软租用Nscale葡萄牙AI数据中心扩增算力

SAP调研显示:中国企业AI投资回报率将达34%

Oracle推出AI数据库26ai版本和自主AI湖仓平台

数字化转型共同主导效果更佳,但需要正确方式

沃尔玛与OpenAI合作推出ChatGPT智能购物功能

全球云市场接近千亿美元,新兴云服务商激增200%