华邦电子加入UCIe产业联盟,支持标准化高性能chiplet接口

2023年2月15日,中国,苏州——全球半导体存储解决方案领导厂商华邦电子今日宣布正式加入UCIe™(Universal Chiplet Interconnect Express™)产业联盟。结合自身丰富的先进封装(2.5D/3D)经验,华邦将积极参与UCIe产业联盟,助力高性能chiplet接口标准的推广与普及。

UCIe产业联盟联合了诸多领先企业,致力于推广UCIe开放标准,以实现封装内芯粒间(chiplet)的互连,构建一个开放的chiplet生态系统,同时也将有助于2.5D/3D先进封装产品的开发。

随着5G、新能源汽车和高速运算等技术的飞速增长,业界对芯片制程与封装技术的要求日益严格。如今,2.5D/3D多芯片封装可实现芯片性能、能效和小型化的指数级提升,已经成为行业聚焦的主流趋势。作为高性能内存芯片的行业领导者,华邦的创新产品CUBE: 3D TSV DRAM可提供极高带宽低功耗,确保2.5D/3D 多芯片封装的能效,并且为客户提供优质的定制化内存解决方案。

加入UCIe联盟后,华邦可协助系统单芯片客户(SoC)设计与2.5D/3D后段工艺(BEOL, back-end-of-life)封装连结。UCIe 1.0规范通过采用高带宽内存接口来提供完整且标准化的芯片间互连环境,促进SoC到内存之间的互连升级,以实现低延迟、低功耗和高性能。总体而言,标准化将助力加速推出高性能产品,为设备制造商和终端用户带来更高价值与收益,从而推动先进多芯片引擎的市场增长。

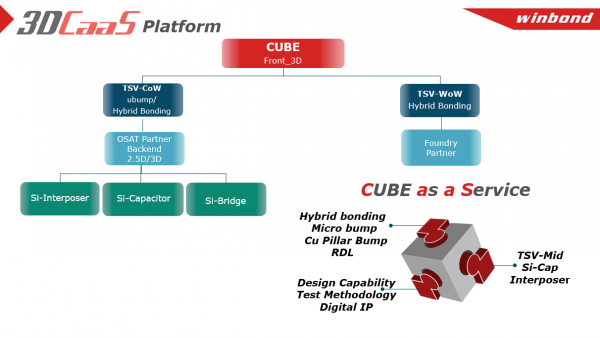

不仅如此,加入UCIe联盟后,华邦提供3DCaaS(3D CUBE as a Service)一站式服务平台,为客户提供领先的标准化产品解决方案。通过此平台,客户不仅可以获得3D TSV DRAM(又名CUBE)KGD内存芯片和针对多芯片设备优化的2.5D/3D 后段工艺(采用CoW/WoW技术),还可获取由华邦的平台合作伙伴提供的技术咨询服务。这意味着客户可轻松获得完整且全面的CUBE产品支持,并享受Silicon-Cap、interposer等技术的附加服务。

华邦电子DRAM产品事业群副总范祥云表示:“2.5D/3D封装技术可进一步提升芯片性能并满足前沿数字服务的严格要求,而随着UCIe规范的普及,我们相信这项技术将在云端到边缘端的人工智能应用中充分发挥潜力,扮演更加重要的角色。”

UCIe联盟主席Debendra Das Sharma博士表示:“作为全球内存解决方案的知名供应商,华邦电子在3D DRAM领域拥有坚实的专业知识,因此我们十分欢迎华邦的加入,并期待华邦为进一步发展UCIe生态做出贡献。”

来源:业界供稿

好文章,需要你的鼓励

Flytrex无人机携手达美乐,可一次性送达两个大号披萨

无人机食品配送服务商Flytrex与全球知名披萨连锁品牌Little Caesars宣布合作,推出全新Sky2无人机,最大载重达4公斤,可一次配送两个大披萨及饮料,满足全家用餐需求。Sky2支持最远6.4公里的配送范围,平均从起飞到送达仅需4.5分钟。首个试点门店已在德克萨斯州怀利市上线,并实现与Little Caesars订单系统的直接集成。

AI助手越权了?南加州大学等机构揭示大模型代理的“权限失控“问题

FORTIS是专门测量AI代理"越权行为"的基准测试,研究发现十款顶尖模型普遍选择远超任务需要的高权限技能,端到端成功率最高仅14.3%。

欧洲最大3D打印公寓楼提前数月竣工

法国社会住房项目ViliaSprint?已正式完工,成为欧洲最大的3D打印多户住宅建筑,共12套公寓,建筑面积800平方米。项目由PERI 3D Construction使用COBOD BOD2打印机完成,整体工期较传统建造缩短3个月,实际打印仅用34天(原计划50天),现场操作人员从6人减至3人,建筑废料率从10%降至5%。建筑采用可打印混凝土,集成光伏板及热泵系统,能源自给率约达60%。

荷兰Nebius团队:给AI“起草员“瘦身,大模型推理速度最高提升5倍的秘密

荷兰Nebius团队提出SlimSpec,通过低秩分解压缩草稿模型LM-Head的内部表示而非裁剪词汇,在保留完整词汇表的同时将LM-Head计算时间压缩至原来的五分之一,端到端推理速度超越现有方法最高达9%。

欧洲最大3D打印公寓楼提前数月竣工

彼亚乔携手迪士尼推出Grogu主题自主跟随货运机器人

Okta将AI智能体安全管理扩展至Amazon Bedrock并向第三方身份提供商开放

苹果13英寸iPad Pro Magic键盘键盘亚马逊历史低价,直降25%

WhatsApp iOS版Liquid Glass界面设计正式向更多用户推送

OpenAI为ChatGPT Pro推出个人财务管理新功能

赛格威全新Xaber 300电动越野摩托车正式开售,最高时速达96公里

OpenAI再度重组高管架构,全力押注AI智能体战场

出门在外也能用!OpenAI 将 Codex 接入 ChatGPT 移动端

Google Gemini应用图标迎来细微配色调整

Synetic在2026嵌入式视觉峰会上发布LYNX计算机视觉SDK

生数科技发布世界动作模型Motubrain,为机器人智能带来"无限可能"