ISSCC 2019大会前瞻:摩尔定律可能正在放缓 但创新则不然

下周将在旧金山开幕的国际固态电路大会(International Solid-State Circuits Conference,ISSCC)已经举办了第66届,在今年大会上你不会看到任何通用处理器芯片的发布,这表明芯片行业正在发生着变化。但在人工智能、5G无线、汽车和医疗等领域,仍然不缺乏创新技术和尖端硬件。

重大微处理器的缺席,似乎反映了两种趋势:首先,随着晶体管接近基本极限,摩尔定律的扩展速度正在放缓。英特尔的10nm Ice Lake将在假期之前面市,而代工厂仍在打磨7nm芯片,因此5nm还要等上数年时间。其次,最新性能上的提升更多地来自于专有加速器而非通用CPU,例如GPU、FPGA和称为ASIC的定制芯片。今年ISSCC大会不乏与汽车、机器人、加密、图形处理和优化问题相关的专有芯片分会场。IBM还将在演讲中提到橡树岭国家实验室和劳伦斯利弗莫尔国家实验室的Sierra,该超级计算机采用Power9 CPU和Nvidia Tesla V100 GPU,是当前世界上最快的TOP500计算机。

Facebook的Yann LeCun将在大会开幕式上谈论在人工智能方面取得持续进展面临的挑战。自2012年ImageNet大赛以来,深度学习领域的大部分进展都来自于监督学习方面,这项技术需要大量的人类标记数据,或强化学习,需要太多的试验才能投入应用中。LeCun认为,未来十年面临的主要挑战将是建造能够像人类一样学习的机器。这种“自监督学习”将需要比现在更强大的硬件,但最终,将会创造出具有某种人类常识的机器。

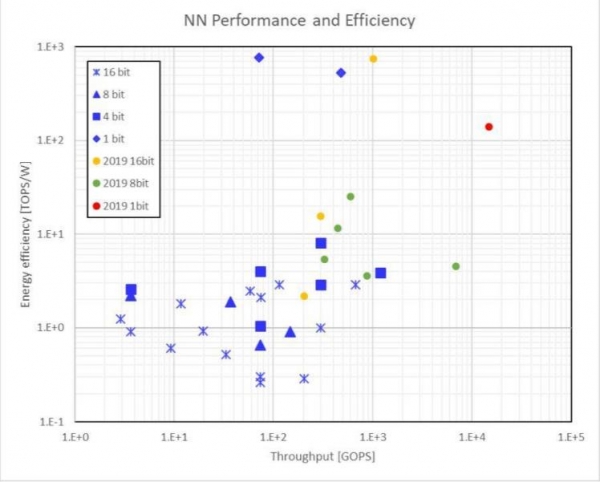

人工智能和机器学习工作负载的增加,催生了具有神经处理单元的移动SoC,例如苹果的A12 Bionic,以及华为用于智能手机和其他边缘设备的HiSilicon Kirin 980。在另一个机器学习的主题大会上,三星将推出双核神经处理器,具有专为8nm工艺设计的1024个MAC单元,能够在0.8瓦下实现每秒6.94万亿次的运算性能。三星表示,该神经处理器架构的速度是之前技术的10倍,关于这个说法,虽然没有更多关于数据格式和算法细节的话,是很难得到验证的,但很明显,神经处理器的性能一直在快速增长,正如下图,对比了自去年ISSCC大会以来机器学习芯片的进展情况。今年的ISSCC大会还会探讨可以处理不同类型人工神经网络(包括用于尖峰神经网络的神经形态芯片)和多位精度的设计以平衡精度和吞吐量的设计。

神经网络处理器的性能和效率正在快速增长中(资料来源:ISSCC 2019)

AI硬件面临的主要挑战之一,是保持这些高度并行处理引擎处于繁忙状态,因为系统无法从内存中读取数据并以足够快的速度写回结果。今年,ISSCC大会有一个下午的论坛,专门讨论面向人工智能和机器学习应用的、以内存为中心的架构,参与讨论的厂商包括ARM、IBM、英特尔、Nvidia和三星等。在高端高速内存方面,高带宽内存(HBM)和GDDDR6正在帮忙解决这个问题,STT-MRAM等新兴的存储内存可以填补DRAM系统内存和闪存固态存储之间的空白。

有一个更新颖的解决方案是当前许多研究的焦点,它完全消除了数据传输,而是在存储阵列中压缩数据。今年ISSCC大会上可能谈及的一些CIM(计算内存)技术包括ReRAM和SRAM宏等。这些设计特别适用于边缘设备的机器学习,因为这些设备具有非常低的延迟,并且在每秒操作性能方面是很高效的。

今年的ISSCC大会你还将看到很多关于传统嵌入式和独立存储设备的新闻。三星和台积电都将展示用于高性能应用的7nm双端口SRAM位单元(双端口RAM允许同时进行多次读写以提高性能)。此外你还将看到一些关于下一代DRAM内存的首次展示,这种内存将增加带宽并降低功耗。三星将展示其第一代10nm级LPDDR5(低功耗DDR5),用于智能手机和其他移动应用,不仅速度更快(每引脚7.4Gbps),而且读写功耗方面相比目前的LPDDR4X降低了21%和33%。竞争对手SK Hynix将推出一款16Gb DDR5芯片,每个引脚的工作速率为6.4Gbps,功耗降低近三分之一。

SK Hynix还将就管理型DRAM封装进行有趣的讨论。该封装将8个芯片与1个控制器相结合,可在模块上达到512GB的容量。首批基于16Gb DDR4芯片(每个封装最多4个)的256GB模块刚刚进入市场,将主流至强可扩展“Cascade Lake”双路服务器的容量推升至6TB。

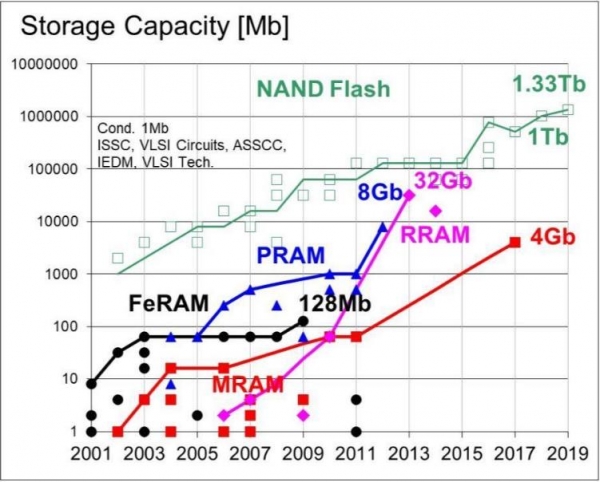

在存储方面,3D NAND闪存和、TLC以及QLC编程技术正在将密度推向新高。西部数据公司(SanDisk)将公布业界密度最高的3D内存堆栈,带有128层和阵列下的外围电路,打造出512Gb的TLC芯片。三星还将推出最新的512Gb TLC芯片,而东芝的96层器件采用QLC技术,将密度提高到每芯片1.33Tb或每平方毫米超过1GB。

随着3D堆叠NAND的快速发展,闪存将继续超越所有新兴竞争对手(资料来源:ISSCC 2019)

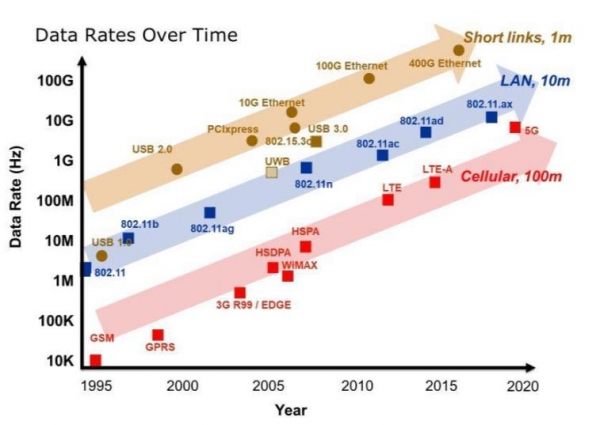

高性能计算、大规模云数据中心、更高速度的4G和5G网络正在所有层面推动对更高速网络的需求。今年的ISSCC大会你将会看到几个最新有线收发器的新闻公告,这些收发器使用PAM-4调制达到或超过100Gbps的速度——包括三款7nm芯片(eSilicon、华为和联发科)和达到创纪录128Gbps的IBM 14nm FinFET设计。所有这些都将有助于满足数据中心内部和数据中心之间更快链接的需求。

在无线WAN方面,高通目前在其X50调制解调器方面具有优势——本月晚些时候在世界移动通信大会上出现在许多首批5G手机中将采用该器件——但其他几家厂商也将紧随其后。在ISSCC大会上,三星将推出14nm基带,支持独立和非独立5G(以及2G、3G和4G),在38.4平方毫米的裸片上提供高达3.15 Gbps的下行速率和1.27Gbps的上行速率,三星将在ISSCC上展示的Exynos Modem 5100芯片组(也包括电源管理芯片)也将采用该技术。英特尔将推出一款28nm 5G收发器,用于低于6GHz的频段和mmWave频段。这是英特尔于2018年末宣布推出的5G芯片组XMM 8160的一个组成部分。XMM 8160支持独立和非独立的5G模式(以及2G、3G、4G和5G),速度最高可达6Gbps。XMM 8160在2019年下半年出货,取代英特尔首个5G芯片组XMM 8060,被英特尔称为“正在成为一款开发平台”。

高性能计算、大规模云数据中心、快速的4G和5G网络在所有层面上推出了对更高速网络的需求(资料来源:ISSCC 2019)

英特尔和其他厂商可能需要更长一段时间才能在微处理器中实现下一个重要的“tick”,但该行业仍然有很多“tock”。正如今年ISSCC大会将呈现的那样,对更快的计算、存储和通信的需求并未放缓,芯片制造商将继续寻找创新的应对方式。

好文章,需要你的鼓励

三星Galaxy S26 Ultra最高优惠435美元,多款智能家居产品同步特惠

本轮优惠涵盖多款热门科技产品:Galaxy S26 Ultra捆绑Galaxy Buds 4 Pro可享325美元折扣,翻新开箱版最高优惠435美元;Galaxy Z Flip 7全新机型立减200美元,翻新版最低仅需701.99美元;谷歌最新款Nest门铃翻新版近百美元优惠;TCL TAB 10 Gen 4安卓平板降至150美元历史低位。三星旗舰产品翻新开箱版正成为当前最具性价比的选择。

AI助手越权了?南加州大学等机构揭示大模型代理的“权限失控“问题

FORTIS是专门测量AI代理"越权行为"的基准测试,研究发现十款顶尖模型普遍选择远超任务需要的高权限技能,端到端成功率最高仅14.3%。

荷兰Nebius团队:给AI“起草员“瘦身,大模型推理速度最高提升5倍的秘密

荷兰Nebius团队提出SlimSpec,通过低秩分解压缩草稿模型LM-Head的内部表示而非裁剪词汇,在保留完整词汇表的同时将LM-Head计算时间压缩至原来的五分之一,端到端推理速度超越现有方法最高达9%。

OpenAI为ChatGPT Pro推出个人财务管理新功能

赛格威全新Xaber 300电动越野摩托车正式开售,最高时速达96公里

OpenAI再度重组高管架构,全力押注AI智能体战场

出门在外也能用!OpenAI 将 Codex 接入 ChatGPT 移动端

Google Gemini应用图标迎来细微配色调整

Synetic在2026嵌入式视觉峰会上发布LYNX计算机视觉SDK

生数科技发布世界动作模型Motubrain,为机器人智能带来"无限可能"

xAI推出编程智能体Grok Build,加入竞争激烈的AI编程赛道

硅谷度假胜地湖太浩面临能源危机,AI热潮推高电价

三星Galaxy S26 Ultra最高优惠435美元,多款智能家居产品同步特惠

华为坤灵三年实践,智能化如何普惠中小企业?

谷歌向"AI优先"智能手机迈出关键一步