IBM观点:芯片制造即将达到极限,但我们的技术有望解决这个难题

IBM公司在无光刻芯片制造方向上取得可喜进展。

IBM公司已经设计出一种新型材料加工与制造工艺,有助于提高7纳米节点以及更小节点芯片的生产效率水平。

蓝色巨人的研究人员正在努力克服“区域选择性沉积”这一新兴领域中的种种挑战,此项技术有望克服光刻技术的限制,从而利用7纳米制程工艺在芯片上创建图案。

Semi Engineering对于光刻图案做出了简洁说明,同时亦解读了为何区域选择性沉积技术在7纳米制程领域拥有如此光明的发展前景(https://semiengineering.com/what-happened-to-selective-deposition/,英文原文)。

“多重图案化”等技术的介入,有助于确保集成电路的规模不断扩展。然而,随着芯片由28纳米制程缩小至7纳米制程,芯片制造商无疑需要面对更多且功能且特征更复杂的分层,且特征必须更精确地放置在对应图案之上。

这些特征需要在不同层之间保持对齐,一旦无法保持对齐,就会导致“边缘放置错误”(简称EPE)。英特尔公司光刻技术专家Yan Borodovsky认为这是一项光刻技术无法解决的挑战,并最终会成为摩尔定律的硬性天花板。

2015年,他曾鼓励业界研究区域选择性沉积技术,而这正是IBM公司研究人员正在探索的领域,且有朝一日可能成为EUV光刻技术的继承性方案。事实上,三星公司已经进行了数十年实验室研究,目前正在尝试将其引入实际生产线。

各晶圆代工厂已经在利用某种形式的选择性沉积技术在器件的金属表面上进行材料沉积。但不同于此,区域选择性沉积要求配合新的工具,旨在于器件之上沉积不同的材料组合——金属沉积于金属上,电介质沉积于电介质上。

IBM公司阿尔马登研究中心研究员Rudy J Wojtecki解释称,IBM的项目希望对这一技术加以改进:

“如果使用传统制造方法,我们需要利用抗蚀剂涂覆基板,而后通过曝光步骤对抗蚀剂进行图案化处理,从而实现图案显影、沉积无机膜,而后去除抗蚀剂以制造出图案化无机材料。”

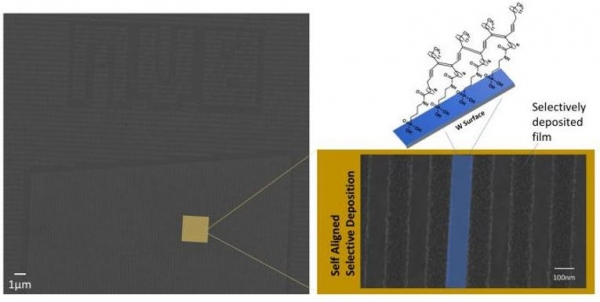

“我们发现了一种更简单的无机薄膜沉积方法,即使用自对准工艺。我们将预先涂覆的基板浸入含有特殊材料的溶液当中,而后将涂覆基板放置于沉积室中,这实际上能够以纳米级可控方式在器件上生长出元件。”

该小组目前使用的为三大主要区域选择性沉积方法之一,名为“原子层沉积”。该方法的重点,在于利用“自聚合单分子层”(简称SAM)。

这种方法可能有助于为新的硬件形式铺平道路,特别是三维结构等能够更好支持人工智能应用程序的硬件形式。

Wojtecki解释称,“一旦我们开发出这一过程的扩展性方法,我们即可在构建下一代硬件时开始采用——包括将其应用于新型人工智能硬件,或者7纳米技术节点或者更小技术节点的器件制造流程。”

IBM公司并不是唯一一家着力开发区域选择性原子层沉积技术的企业,不过Wojtecki认为他将能够为具有苛刻要求的应用定制化学结构,从而使得这种“新聚合、材料与表征方法”的开发最终具备可扩展能力。

来源:至顶网服务器频道

好文章,需要你的鼓励

CES上杨元庆首谈AGI,碾压人类的叙事不会让AI更聪明

很多人担心被AI取代,陷入无意义感。按照杨元庆的思路,其实无论是模型的打造者,还是模型的使用者,都不该把AI放在人的对立面。

MIT递归语言模型:突破AI上下文限制的新方法

MIT研究团队提出递归语言模型(RLM),通过将长文本存储在外部编程环境中,让AI能够编写代码来探索和分解文本,并递归调用自身处理子任务。该方法成功处理了比传统模型大两个数量级的文本长度,在多项长文本任务上显著优于现有方法,同时保持了相当的成本效率,为AI处理超长文本提供了全新解决方案。

Gmail新增Gemini驱动AI功能,智能优先级和摘要来袭

谷歌宣布对Gmail进行重大升级,全面集成Gemini AI功能,将其转变为"个人主动式收件箱助手"。新功能包括AI收件箱视图,可按优先级自动分组邮件;"帮我快速了解"功能提供邮件活动摘要;扩展"帮我写邮件"工具至所有用户;支持复杂问题查询如"我的航班何时降落"。部分功能免费提供,高级功能需付费订阅。谷歌强调用户数据安全,邮件内容不会用于训练公共AI模型。

华为研究团队突破代码修复瓶颈,8B模型击败32B巨型对手!

华为研究团队推出SWE-Lego框架,通过混合数据集、改进监督学习和测试时扩展三大创新,让8B参数AI模型在代码自动修复任务上击败32B对手。该系统在SWE-bench Verified测试中达到42.2%成功率,加上扩展技术后提升至49.6%,证明了精巧方法设计胜过简单规模扩展的技术理念。

联想集团混合式AI实践获权威肯定,CES期间获评“全球科技引领企业”

CES上杨元庆首谈AGI,碾压人类的叙事不会让AI更聪明

CES 2026 | 重大更新:NVIDIA DGX Spark开启“云边端”模式

Gmail新增Gemini驱动AI功能,智能优先级和摘要来袭

研究发现商业AI模型可完整还原《哈利·波特》原著内容

Razer在2026年CES展会推出全息AI伴侣项目

CES 2026:英伟达新架构亮相,AMD发布新芯片,Razer推出AI奇异产品

通过舞蹈认识LimX Dynamics的人形机器人Oli

谷歌为Gmail搜索引入AI概览功能并推出实验性AI智能收件箱

DuRoBo Krono:搭载AI助手的智能手机尺寸电子阅读器

OpenAI推出ChatGPT Health医疗问答功能

Anthropic寻求3500亿美元估值融资100亿美元