英特尔Agilex 7 FPGA R-Tile现已量产,为CPU提供行业领先的带宽

在技术创新的推动下,从边缘计算到云的新连接和处理模型也在高速发展,随之而来的,则是对灵活硬件解决方案与日俱增的需求。随着市场上对带宽的要求不断增加,对更快、更灵活的设备的需求也日益迫切。而于近期推出的英特尔Agilex® 7 FPGA R-Tile,凭借其高带宽接口和灵活的可编程逻辑,能够满足行业发展需求。目前,基于R-Tile的英特尔Agilex 7 FPGA正在量产。

近年来,FPGA 加速器在市场上的应用率稳步增长,而随着配备R-Tile的FPGA 的推出,更高性能的加速器也随之而来。FPGA 加速器可以将任务从主机CPU 卸载,释放CPU核心并减少总功耗,实现总拥有成本(TCO)的节省。如您作为最终用户、IT专家或云服务提供商,且尚未探索使用FPGA加速器,现在则是一个良好的尝试时机。

- 使用FPGA加速器的云服务提供商可以支持更多用户,并释放更多CPU核心给更多的用户,从而获得更多服务收入。

- 利用FPGA加速器的原始设备制造商可以节省成本并减少功耗。

英特尔Agilex® 7 FPGA产品系列已应需设计以满足市场要求,而且基于R-Tile的版本已经开始量产。

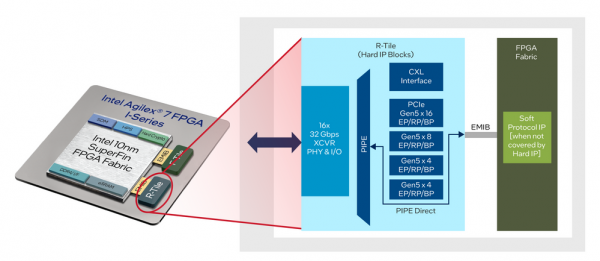

英特尔Agilex® 7 FPGA采用了异构多芯片架构,其中位于中心位置的FPGA芯片与收发器芯粒通过英特尔的嵌入式多芯片互连桥接(EMIB)封装技术相连。每个芯粒或区块都是一个小型集成电路芯片,包含一组明确定义的硬化功能子集。这些芯粒使得成本高效的,封装内部高密度互连异构芯片成为现实。通过采用异构多芯片架构和芯粒的设计,英特尔能够在单个设备中提供多样化的功能和灵活性,以满足不同应用的需求。这种方法消除了使用多个设备进行连接的需要,简化了系统设计和集成的复杂性,并提供了更高的可扩展性和性能。

诸多英特尔Agilex® 7 FPGA封装组合中都包含了R-Tile芯粒,旨在与高性能CPU 连接时可提供行业领先的带宽。R-Tile芯粒结合了PCIe 5.0 x16和CXL 1.1/2.0 的硬化知识产权(IP)块和软件IP代码,为网络、云计算、数据中心、科学计算等诸多领域提供了高度灵活的解决方案。如下是R-Tile支持的关键技术特性列表:

图1. 英特尔Agilex® 7 FPGA与R-Tile模块的图解

|

R-Tile特性(每个区块) |

描述 |

|

PCle 5.0 x16 Up to32GT/sper lane 1x16EP/RP 2x8EP/RP 4 x4 RP 端点(EP)Root Port(RP)PIPE直接事务层旁路/切换选项 虚拟化&确切时间选项 |

灵活的、多功能的PCIe 5.0硬化IP模块,允许您在高性能FPGA设计中创建端点、根端口、交换机或定制的PCIe接口。 Intel Agilex 7 FPGA R-Tile是唯一具备完整的50x16数据速率且符合PCI-SIG标准的设备。 |

|

CXL1.1/2.0x16 Up to 32 GT/s per lane 1x16 EP Supports CXL Type1 Type2 with DCOH and Type 3. |

这是FPGA行业中首款具有CXL硬化IP的设备,可以以全速率管理链接并预处理CXL数据包。软件协议IP管理CXL事务层功能。图形用户界面(GUI)允许进行以下自定义操作:

与第四代英特尔® 至强® 可扩展处理器进行了广泛的验证和互操作性测试。CXL认证待定,将在Compute Express Link协会的活动中进行。 预计支持选定的CXL 2.0功能,待验证、互操作性测试和与未来CPU的合格性确认后提供支持。 |

表1. 英特尔Agilex® 7 FPGA R-Tile关键特性

符合量产要求的R-Tile版本标志着英特尔Agilex® 7 FPGA I系列设备中四种不同封装下的七种逻辑密度的器件进入量产阶段。这样一来,客户就能够在他们的新设计中充分利用英特尔Agilex® 7 FPGA提供的性能和功耗领先优势。基于英特尔10纳米工艺技术,英特尔Agilex® 7 FPGA可编程逻辑和R-Tile芯粒充分利用英特尔强大的供应链优势,以及先进的制造和测试能力,能够在标准交货期内提供量产解决方案。一旦英特尔Agilex® 7 FPGA M系列R-Tile的样品过渡到量产阶段,将具备更多设备密度和封装选项。

将R-Tile的功能与其他的英特尔Agilex® 7 FPGA芯粒(如最近发布的F-Tile)相结合,可以创建出适用于下一代加速器(如SmartNIC、IPU和计算存储解决方案)的灵活高性能FPGA。

来源:业界供稿

好文章,需要你的鼓励

拆解视频大语言模型评测基准:知识、空间感知还是真正的时序理解?苹果公司研究团队带来新分析框架

这项来自苹果公司的研究揭示了视频大语言模型评测的两大关键问题:许多测试问题不看视频就能回答正确,且打乱视频帧顺序后模型表现几乎不变。研究提出VBenchComp框架,将视频问题分为四类:语言模型可回答型、语义型、时序型和其他类型,发现在主流评测中高达70%的问题实际上未测试真正的视频理解能力。通过重新评估现有模型,研究团队证明单一总分可能掩盖关键能力差距,并提出了更高效的评测方法,为未来视频AI评测提供了新方向。

差分信息:一种信息论视角下理解偏好优化的新方法 - KAIST AI研究团队突破性解读

这篇来自KAIST AI研究团队的论文提出了"差分信息分布"(DID)这一创新概念,为理解直接偏好优化(DPO)提供全新视角。研究证明,当偏好数据编码了从参考策略到目标策略所需的差分信息时,DPO中的对数比率奖励形式是唯一最优的。通过分析DID熵,研究解释了对数似然位移现象,并发现高熵DID有利于通用指令跟随,而低熵DID适合知识密集型问答。这一框架统一了对DPO目标、偏好数据结构和策略行为的理解,为语言模型对齐提供理论支持。

VidText:视频文本理解的全面评估新基准,打造视觉文本与上下文交互的研究新高度

VidText是一个全新的视频文本理解基准,解决了现有评估体系的关键缺口。它涵盖多种现实场景和多语言内容,提出三层评估框架(视频级、片段级、实例级),并配对感知与推理任务。对18个先进多模态模型的测试显示,即使最佳表现的Gemini 1.5 Pro也仅达46.8%平均分,远低于人类水平。研究揭示输入分辨率、OCR能力等内在因素和辅助信息、思维链推理等外部因素对性能有显著影响,为未来视频文本理解研究提供了方向。

ZeroGUI:零人工成本下自动化在线GUI学习的突破性研究

ZeroGUI是一项突破性研究,实现了零人工成本下的GUI代理自动化在线学习。由上海人工智能实验室和清华大学等机构联合开发,这一框架利用视觉-语言模型自动生成训练任务并提供奖励反馈,使AI助手能够自主学习操作各种图形界面。通过两阶段强化学习策略,ZeroGUI显著提升了代理性能,在OSWorld环境中使UI-TARS和Aguvis模型分别获得14%和63%的相对改进。该研究彻底消除了传统方法对昂贵人工标注的依赖,为GUI代理技术的大规模应用铺平了道路。

IXD0579M高压侧和低压侧栅极驱动器提供紧凑型即插即用解决方案

向下扎根求力量,向上迸发促未来|2025 友达数位智能制造年度峰会圆满落幕!

新一代Dell PowerEdge机架式服务器助力数据中心加速进化

站在下一次浪潮的最前沿,微软眼中的“开放智能体网络”

互联网女皇玛丽·米克尔刚发布了一份340页的《人工智能趋势报告》,这里总结了10个核心观点

吴恩达LangChain对话:别纠结Agent定义,成功的智能体往往从线性工作流开始,Vibe Coding这个概念充满误导

是否应该为 Google 的 Veo 3 支付 Gemini Ultra 费用来制作 AI 视频?我的体验告诉你答案

KO 满血版DeepSeek?AM-Thinking-V1,32B干翻一众千亿级大模型

字节Seed团队绝地翻盘,发现多模态模型也有涌现时刻,开源BAGEL模型

物理世界如何实现AGI?前空中客车CTO红杉访谈:我们的愿景是让AI设计人类无法设计的系统,从星际飞船到戴森球

法国政府正式出价4.1亿欧元收购Atos精简后的高性能计算资产

理解 GPU 服务器及其在数据中心中的角色