5纳米芯片推力电池续航能力提升 原创

至顶网服务器频道 06月07日 新闻消息(文/编译):

本周一(6月5日)在东京VLSI技术与电路2017研讨会上公布的最新架构,可谓IBM公司过去十年以来同GlobalFoundries、三星以及其它多家设备供应商合作开发而成的关键性成果。根据研究人员们的介绍,相较于FinFET,这套新架构的运行功耗更低。

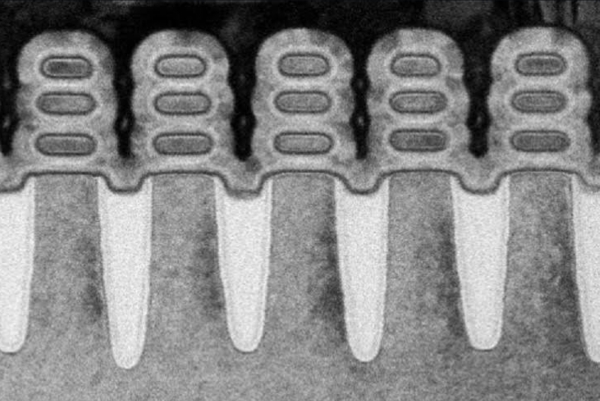

IBM/GlobalFoundries/三星共同打造的革命性5纳米纳米片晶体管,其凭借着四路多面栅能够为手机设备提到2到3天的电池续航能力。

该联盟解释称,这项革命性突破应该能够使得智能手机以及其它类似的电池供电型移动设备在一次充电后正常运行2到3天; 另外,其还能够提高人工智能(简称AI)、虚拟现实甚至是超级计算机的性能水平。

研究人员们指出,在成功开发出包含200亿个晶体管的7纳米测试芯片之后不到两年当中,他们已经在这块只有指甲大小且拥有四重多面栅的芯片中塞进多达300亿个晶体管。测试结果表明,与目前最为先进的10纳米芯片相比,其性能提升了40%(与7纳米FinFET基本相同),或者将功耗水平降低75%。

根据IBM公司的说明,这项突破性5纳米技术能够利用更为强大的性能提升认知计算能力,改善云计算与深度学习的数据吞吐量水平并帮助各类移动物联网(简称IoT)设备获得更低功耗与更高电池续航时长。

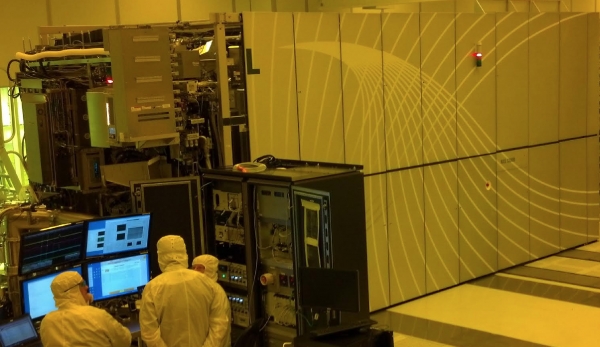

IBM公司的科学家们在位于纽约州奥尔巴尼的纽约州立大学纳米科学与纳米工程技术综合中心内对5纳米硅纳米片晶体管晶圆进行测试,旨在评估这项业界首创的制程工艺。

(图片来源: 纽约州立大学)

为了实现技术突破,该技术联盟必须克服干扰EUV(即极紫外线)光刻工艺的各类问题——事实上,此项光刻技术已经被应用于7纳米FinFET芯片的制造当中。EUV除了拥有波长较短这一优势之外,研究联盟还发现了在芯片设计与制造阶段中不断调整其纳米片宽度的办法。研究人员们表示,FinFET的性能与功率不具备微调可能性——这主要是由于FinFET受翅片高度的限制而无法增加通过电流,因此不能提供更高的性能。

科学家与工程师在位于纽约州奥尔巴尼的纳米技术综合中心之内监督EUV光刻工具在此番业界首创工艺中的实际使用,旨在确保由此构建起5纳米硅纳米片芯片。

(图片来源: 纽约州立大学)

IBM公司认为,其纳米片结构在历史地位上将等同于单单元DRAM、化学放大光电抗蚀剂、铜互连、硅绝缘体、应变材料、多核心处理器、渲染光刻、高k电介质、嵌入式DRAM、3D芯片堆叠以及气隙绝缘子等技术成果。

Globalfoundries公司首席技术官兼全球研发工作负责人Gary Patton用“开创性”来形容此项公告,并表示该公司正在积极追求5纳米以及下一代芯片制造技术。

位于纽约州奥尔巴尼的纽约州立大学纳米科学与纳米工程技术综合中心亦为IBM、GlobalFoundries以及三星的5纳米纳米片晶体管架构的研发工作作出了巨大贡献。

好文章,需要你的鼓励

Anthropic发布入门级Claude Haiku 4.5混合推理模型

Anthropic发布了面向成本敏感用户的Claude Haiku 4.5大语言模型,定价为每百万输入令牌1美元,输出令牌5美元,比旗舰版Sonnet 4.5便宜三倍。该模型采用混合推理架构,可根据需求调整计算资源,支持多模态输入最多20万令牌。在八项基准测试中,性能仅比Sonnet 4.5低不到10%,但在编程和数学任务上超越了前代Sonnet 4。模型响应速度比Sonnet 4快两倍以上,适用于客服聊天机器人等低延迟应用场景。

ByteDance推出Seedream 4.0:AI图像生成的新纪元,一秒生成4K图片的超级引擎

字节跳动发布Seedream 4.0多模态图像生成系统,实现超10倍速度提升,1.4秒可生成2K高清图片。该系统采用创新的扩散变换器架构,统一支持文字生成图像、图像编辑和多图合成功能,在两大国际竞技场排行榜均获第一名,支持4K分辨率输出,已集成至豆包、剪映等平台,为内容创作带来革命性突破。

微软与Nscale签署价值240亿美元数据中心合同

英国初创公司Nscale将为微软建设四个AI数据中心,总计部署约20万个GPU,合同价值高达240亿美元。首个数据中心将于明年在葡萄牙开建,配备1.26万个GPU。德州数据中心规模最大,将部署10.4万个GPU,容量从240兆瓦扩展至1.2吉瓦。所有设施将采用英伟达最新Blackwell Ultra显卡。

AI系统透明度新突破:红帽团队提出智能安全卡让AI系统更可信

红帽公司研究团队提出危险感知系统卡(HASC)框架,为AI系统建立类似"体检报告"的透明度文档,记录安全风险、防护措施和问题修复历史。同时引入ASH识别码系统,为AI安全问题建立统一标识。该框架支持自动生成和持续更新,与ISO/IEC 42001标准兼容,旨在平衡透明度与商业竞争,建立更可信的AI生态系统,推动行业协作和标准化。

Anthropic发布入门级Claude Haiku 4.5混合推理模型

微软与Nscale签署价值240亿美元数据中心合同

谷歌将在印度建造150亿美元AI数据中心枢纽

Eightfold联合创始人获3500万美元融资,打造员工数字孪生AI查询平台

新加坡交通部门采用光纤局域网升级关键铁路基础设施

Oracle推动智能体AI在ERP和供应链领域应用

微软英伟达等巨头400亿美元收购数据中心推高AI泡沫

Google Veo 3.1视频生成模型升级,图像转视频能力增强

中国交换生、世界前50击剑手、Anthropic研究员Sholto:如何打造出最强编码模型,AGI瓶颈是错觉,品味是AI好坏关键

人工智能商业落地“大考”,研华交出了一份怎样的产业答卷?

英国量子计算发展面临挑战,专家呼吁政府加大支持力度

Infor深耕亚太市场:云计算与AI驱动制造业数字化转型