除了英伟达,ARM NEOVERSE V2核心还有没有其他受众?

最近一段时间,Hot Interconnects、Hot Chips、Google Cloud Next和Meta Networking@Scale等重量级会议先后亮相。借此机会,我们打算通过本文以更有条理的方式对资讯亮点做一番整理,聊聊并深入分析我们听到和看到的这些丰富内容。

这一次,我们将关注重点放在即将重新上市的Arm“Demeter”Neoverse V2核心。

如果Demeter核心出现在五年、甚至是十年之前,那肯定会成为引爆业界的大新闻。毕竟对于很多想要开发Arm服务器芯片的厂商来说,设计出优秀核心确实非常困难。而从今年Hot Chips上亮相的“Genesis”计算子系统(CSS)来看,其实设计一款好的处理器也绝非易事。超大规模基础设施厂商和云服务商一直想要针对其工作负载采用大规模定制化处理器。相较于直接采用现成的处理器设计,这些大企业和面对特定工作负载需求的用户当然希望计算方案能够更贴合自身实际。

但处理器经销商(请注意,经销商跟制造商不是一回事)无法提供大规模定制产品,毕竟为每一代芯片架构开发多种变体的成本非常高昂。而我们所看到的所谓“变体”,大多只是开启或关闭某些设计中的固有功能,属于为了顺应芯片良品率不足的无奈之举。通过这种刻意控制性能水平的方式,厂商可以人为拉开产品差距、最大化业务收入。

Demeter核心是首款实现了2021年3月公布的Armv9架构的核心,也是迄今为止Arm为服务器平台设计的最强核心。正因为如此,英伟达才会仅对该核心及其他组件开放72核“Grace”服务器CPU授权,使其成为英伟达系统架构中的组成部分。这套方案属于支持传统高性能计算(HPC)仿真与建模工作负载的纯CPU计算,并可提供辅助内存与计算容量。凭借四个128位SVE2矢量引擎,Demeter核心成为一套可运行经典HPC工作负载及某些AI推理工作负载(但能够承受的规模有限,所以大语言模型应该不在此列)的强劲引擎,在某些情况下甚至可用于AI模型的重新训练。如果最终在设计中将核心数量设置为16到256个,那么其算力规模自然也将水涨船高。

但最让我们好奇的是,除了英伟达之外,还有哪些厂商愿意在自家CPU设计中使用Demeter核心。

AWS很可能会在其内部自研的下一代Graviton 4服务器处理器中采用V2核心,毕竟当前Graviton 3处理器使用的就是“Zeus”V1核心。阿里巴巴在自主研发的128核倚天710处理器中使用的则是Neoverse “Perseus”N2核心;如果他们认为未来需要在标准服务器中支持更强的矢量与矩阵数学计算能力,则可在后续倚天芯片中转向V2核心,借此支持愈发普遍且对数学运算能力要求更高的各类AI算法。华为旗下的芯片设计部门海思在其64核鲲鹏920服务器芯片中使用了Arm的Neoverse“Ares”N1核心,出于同样的原因,他们也可能在下代版本中转而采用V2核心。目前还不清楚谷歌传闻正在开发的两款定制化Arm服务器芯片采用什么核心——其中之一据称是与Marvell合作设计,另外一款则纯为内部原研。如果事实证明他们采用的确实是V2,那也完全在情理之中。Ampere Computing已经将其192核“Siryn”AmpereOne芯片中的Arm“Ares”N1核心替换为自家原研核心(我们暂时称其为A1)。印度高级计算发展中心(C-DAC)也针对高性能计算工作负载构建了自己的“Aum”处理器,其基于Arm的Neoverse V1核心。而根据之前的报道,富士通、Arm和日本RIKEN实验室联合为“富岳”超级计算机采用了48核A64FX处理器,其中使用的512位矢量定制Arm核心虽然专为A64FX所设计,但也可以被视为一种Neoverse V0核心。

我们还想知道,除了在Hot Chips 2023上公布N2核心芯片之外,Arm为什么没有立即推出基于V2核心的CSS服务器芯片设计。或者说,为什么不能在CSS设计中同时使用N2和V2两种核心?关于这个问题,我们的猜测是不少数据中心运营商更看重性价比方面的优化,对于矢量计算能力的需求相对不是特别强;当然,这里关于软件和工作负载的推断是否正确仍有待观察。但AWS选择V1、英伟达选择V2应该传递出了明确的信号。Ampere Computing的A1核心在矢量计算方面更接近N2核心,其搭载两个128位引擎,明显是认为没必要在云端设置太多矢量计算核心。

前有V2飞弹,现有V2核心

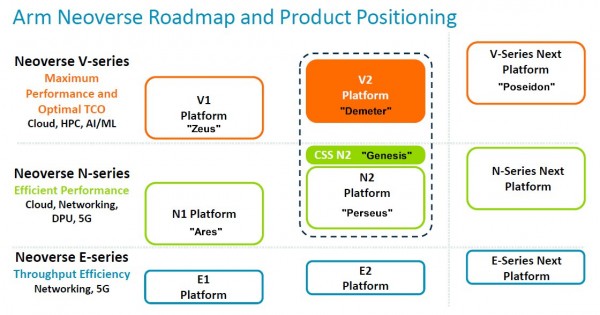

Arm于2020年9月宣布将Neoverse核心和CPU设计划分为三大类别,首先是主线N系列核心(重点关注整数性能),第二是剥离出来的V系列高性能核心(搭载双矢量引擎),最后则是入门级E系列核心(重点关注能效和边缘应用场景)。多年以来,该路线图已经历多轮扩展和更新,最新一代路线图(即引入了N2平台的CSS子系统变体)前段时间正式登陆Hot Chips:

为了显得更亲切,我们在图表中添加了各核心和平台的代号。

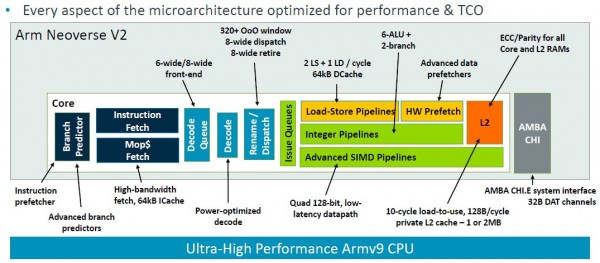

Arm研究员兼首席CPU架构师Magnus Bruce在Hot Chips介绍了V2平台,解释了该架构与Zeus V1平台间的区别。具体细节,请参考以下图表:

Bruce解释道,“整个管线的运行基础,在于其中的提前运行分支预测器。这个分支预测器充分的是指令预取器,负责把提取与分支区分开来。这样的大型分支预测结构能够覆盖相当一部分现实服务器工作负载。我们在其中使用到发出后才进行读取的物理寄存器文件,这样就能让发出队列拥有极大的规模,且不会增加数据存储负担。只有这样,我们才能解锁ILP(即指令级并行性)。我们使用低延迟的私有L2缓存、低延迟L1与私有L2缓存,再配合最先进的预取算法和主动存储到加载转发,借此将核心上的冒泡和停顿减至最少。此外,系统的动态反馈机制还允许核心调节这种主动性,防止系统拥塞。正是凭借这些基本概念,我们才能扩大机器的宽度和深度,同时继续保持管线足够短小以实现较快的错误预测恢复速度。”

更重要的是,这是一款基于Armv9、但又旨在颠覆该架构的实现。与之前十多年来长期用于定义Arm芯片的多代Armv8架构相比,新方案在性能、安全性和可扩展性方面均实现了增强。

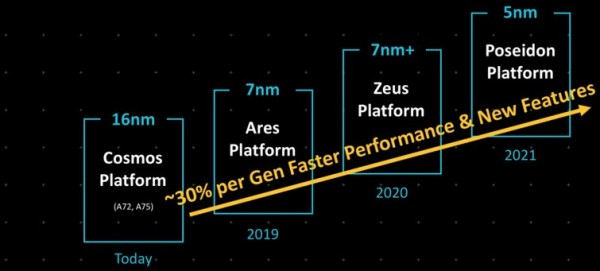

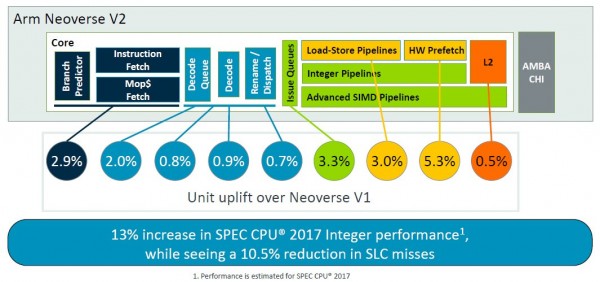

V2芯片的架构调整非常微妙,但显然也颇为有效。可我们可以看到,区区13%的性能提升距离Arm在2019年定下的每时钟指令数(IPC)30%的提升目标还有很长的路要走:

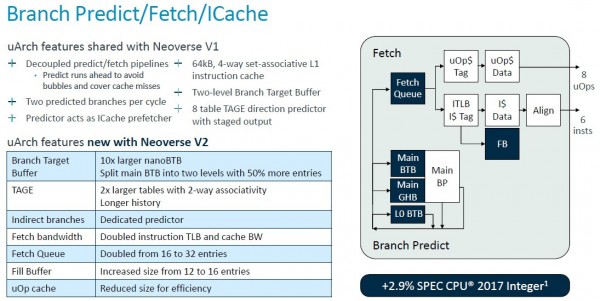

先抛开这个问题,下面我们通过图表具体看看V2核心的分支预测器、获取单元和L1缓存的设计变化:

如大家所见,V1核心中的很多功能都被照搬到了V2核心,但后者也不乏更多更新。其队列、表和带宽大多实现了倍增,只有微操作缓存在转向V2时反而有所减少。根据芯片模拟器对V1和V2建模进行的SPEC CPU 2017整数基准测试,V2核心调整让每时钟指令数增加了约2.9%。

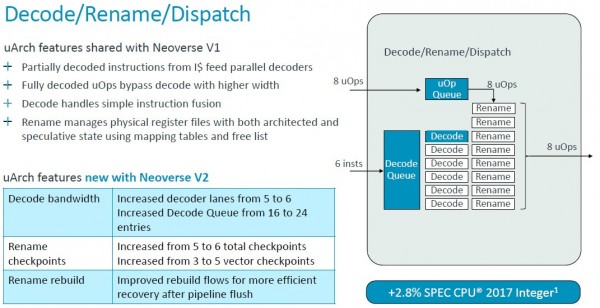

同样的,V1核心微架构上的一些解码和指令分派优势也被V2核心直接继承,同时对解码器通道和队列做出了增强。总体效果就是每时钟指令数提高了2.9%,结果同样来自SPEC CPU 2018整数基准测试。(每时钟指令数往往需要由混合测试进行计算,单凭SPEC CPU测试可能不够准确,但我们目前就只有这份结果,所以姑且用之。)

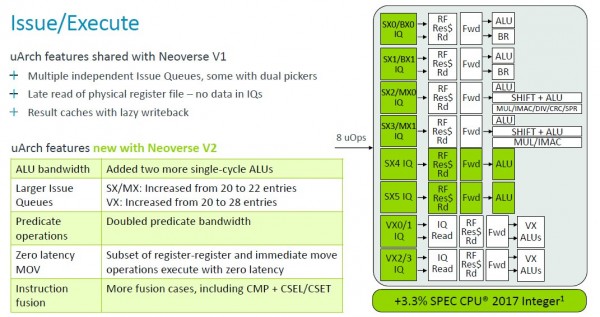

在V2核心上,Arm架构师又添加了两个单周期算术逻辑单元(ALU),增加了发出队列的大小,并将谓词运算符的带宽加倍。这些调整配合其他改进,让核心在2.8 GHz的频率下将性能进一步提升3.3%。

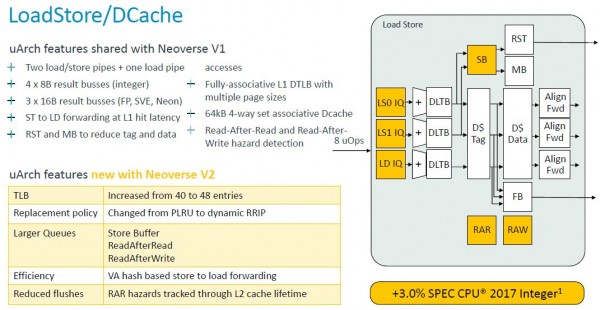

与V1核心一样,V2核心设有两条加载/存储管线和一条加载管线,但表后备缓冲区(TLB)上的条目从40个增加到48个,各种存储和读取队列也变得更大。

这些调整配合其他改进,又让V2核心性能再度增长3%。

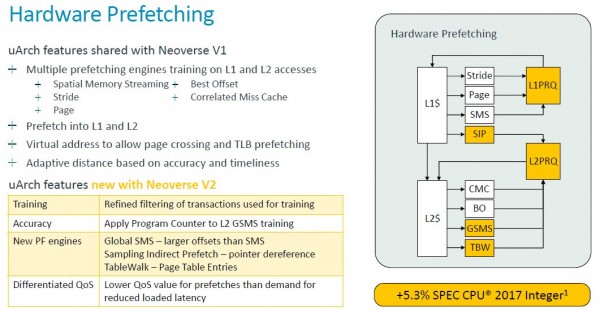

Arm架构师实现的最大性能提升,则是通过硬件预取数据来实现:

Bruce解释道,“Neoverse V1已经具备了最先进的预取功能。”而在对预取增强功能做简单介绍时,他思考半晌给出了这样的说明:“通过对L1和L2未命中进行多引擎训练,并将结果预取至L1和L2缓存中,我们的预取器能够主要使用虚拟地址来实现页面交叉,借此使其充当TLB预取。预取器使用来自互连的动态反馈及CPU内部的准确性/及时性测量指标来调节主动性。V2继续沿用V1的硬件基础,但改进了训练以增强过滤效果并提高操作准确性,能够在更多预取器中使用程序计数器来实现更好的关联和防混叠效果。V2还添加了新的预取引擎。L2获得了全局空间内存流引擎,借此增加了所能覆盖的预取器领衔范围,而且相较之前的标准SMS引擎实现了很大改进。我们又添加了一个采样间接预取器,用于处理指针解除引用的情况。但到这里,所有这些新增的预取器及其主动性设置又会造成新的潜在系统拥塞,特别是影响到系统级缓存或DRAM等共享资源。为此,我们对需求和预取提供了差异化的QoS级别,这样既能主动执行预取,又不会给需求请求带来额外的加载延迟。预取动态反馈机制能够将预取器的主动性调节至合理的可持续水平。以上种种调整让sepc管理器增加了5.3%,但同时让SLC未命中率降低了8.2%。也就是说,我们能够用更少的DRAM流量获取更高性能。”

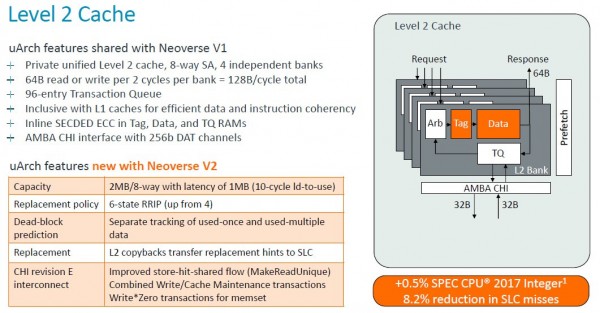

下面来看L2缓存如何发挥其魔力:

将L2缓存加倍并没有对性能产生太大影响,但系统级缓存未命中率的降低确实间接提高了性能水平。

以下是每时钟指令数的提升总和:

各数值之间是加法、而非乘法关系,V2核心的整数性能最终提升了13%。当然,这是建模计算的结果,借代表在SPEC CPU 2017整数基准测试中的表现。此外,V2核心将系统级缓存的总体未命中率降低了10.5%。

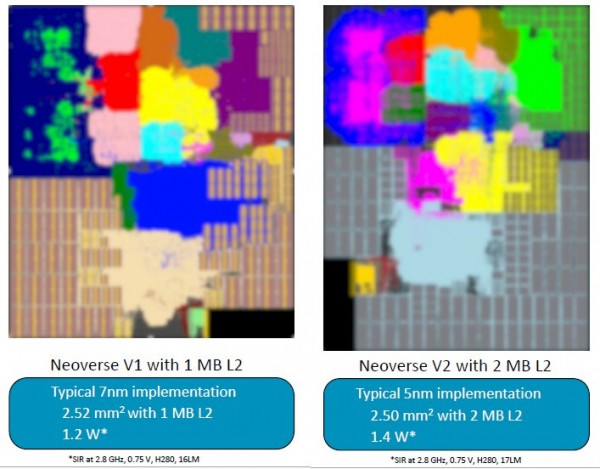

每当有新的核心或者芯片问世,具体产品都会根据性能、功耗和尺寸等指标间的综合作用进行分级。下面来看V1和V2核心的综合情况:

采用7纳米制程工艺的V1核心尺寸为2.5平方毫米,L2缓存为1 MB,功耗约为1.2瓦。V2核心的尺寸稍小一些,L2缓存倍增至2 MB,功耗提高了18%。所有指标均在2.8 GHz时钟速率下做标准化比较。

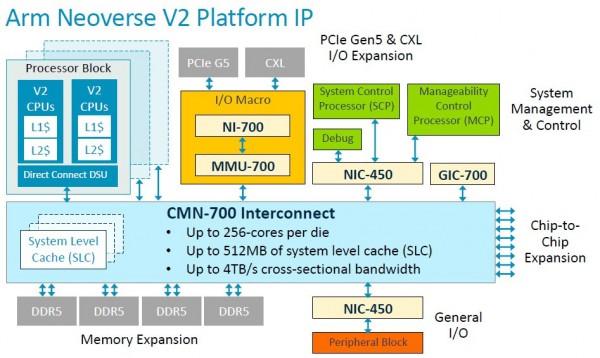

当然,V2所代表的不只是核心,更是一整套可供授权的平台规范:

借助CMN-700互连,获得Arm许可的厂商可以构建起至高256核心、512 MB系统缓存的V2 CPU。该互连可在网格上的所有核心、内存和I/O控制器之间提供4 TB/秒的截面带宽。

V2核心的大部分演示都集中在整数性能层面。但在演讲后的问答环节中,Bruce也介绍了不少关于矢量性能的有趣内容。V1核心搭载两个256位SVE1矢量引擎,但V2核心则调整为四个128位SVE2矢量引擎。根据Brice的说明,这样做是因为将混合精度数学运算分配给四个单元、要比分配给两个单元更容易(应该也更高效)。

但正如我们在文章开头所说,除了英伟达和可能的AWS之外,还有谁会愿意申请V2核心的授权许可?这个问题真的很难回答,毕竟V2核心的潜在受众基本上都已经在自主设计架构,似乎没有理由非要花钱选择这样一种CSS变体。

好文章,需要你的鼓励

AI投资有望在2026年获得真正回报的原因解析

尽管全球企业AI投资在2024年达到2523亿美元,但MIT研究显示95%的企业仍未从生成式AI投资中获得回报。专家预测2026年将成为转折点,企业将从试点阶段转向实际部署。关键在于CEO精准识别高影响领域,推进AI代理技术应用,并加强员工AI能力培训。Forrester预测30%大型企业将实施强制AI培训,而Gartner预计到2028年15%日常工作决策将由AI自主完成。

北大学者革新软件诊断方式:让代码问题的“病因“无处遁形

这项由北京大学等机构联合完成的研究,开发了名为GraphLocator的智能软件问题诊断系统,通过构建代码依赖图和因果问题图,能够像医生诊断疾病一样精确定位软件问题的根源。在三个大型数据集的测试中,该系统比现有方法平均提高了19.49%的召回率和11.89%的精确率,特别在处理复杂的跨模块问题时表现优异,为软件维护效率的提升开辟了新路径。

2026年软件定价大洗牌:IT领导者必须知道的关键变化

2026年软件行业将迎来定价模式的根本性变革,从传统按席位收费转向基于结果的付费模式。AI正在重塑整个软件经济学,企业IT预算的12-15%已投入AI领域。这一转变要求建立明确的成功衡量指标,如Zendesk以"自动化解决方案"为标准。未来将出现更精简的工程团队,80%的工程师需要为AI驱动的角色提升技能,同时需要重新设计软件开发和部署流程以适应AI优先的工作流程。

德国达姆施塔特工业大学团队首次揭秘:专家混合模型AI的“安全开关“竟然如此脆弱

这项由德国达姆施塔特工业大学领导的国际研究团队首次发现,当前最先进的专家混合模型AI系统存在严重安全漏洞。通过开发GateBreaker攻击框架,研究人员证明仅需关闭约3%的特定神经元,就能让AI的攻击成功率从7.4%暴增至64.9%。该研究揭示了专家混合模型安全机制过度集中的根本缺陷,为AI安全领域敲响了警钟。

稚晖君发布全球最小全身力控人形机器人,上纬启元开启个人机器人时代

2026年软件定价大洗牌:IT领导者必须知道的关键变化

Linux 在 2026 年将势不可挡,但一个开源传奇可能难以为继

CES 2026趋势展望:全球最大科技展五大热门话题预测

人工智能时代为何编程技能比以往更重要

AI颠覆云优先战略:混合计算成为唯一出路

谷歌发布JAX-Privacy 1.0:大规模差分隐私机器学习工具库

谷歌量子AI发布新型优化算法DQI:量子计算优化领域的重大突破

缓解电动汽车里程焦虑:简单AI模型如何预测充电桩可用性

Titans + MIRAS:让AI拥有长期记忆能力

Gemini为STOC 2026大会理论计算机科学家提供自动化反馈

夸克AI眼镜持续升级:首次OTA,支持89种语言翻译