小芯片生态系统正逐步迎来融合

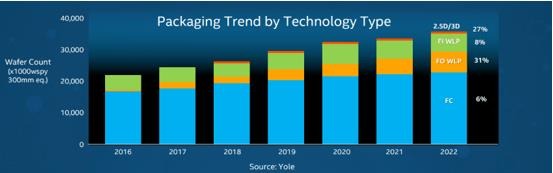

开放式芯片生态系统正在逐步发展当中渐渐迎来融合,如今在系统级封装(SiP)当中对多家供应商的芯片组进行异构集成已经不再只是空谈。

小芯片的出现,代表着芯片行业通过暴力扩展弥补性能增量不足的一类重要尝试;而这一切都与重要的时代背景分不开,即摩尔定律的放缓。虽然包括英特尔、Marvell以及初创企业zGlue在内的各家芯片公司,外加思科等系统厂商都在创建自有芯片生态系统领域取得了一定的成功,但迄今为止的所有努力仍然高度信号于专有型多芯片接口。

要想开发一套完整的全行业开放式小芯片生态系统,从而帮助设计人员将来自多家供应商的“同类最佳”芯片组件封装于一处,不仅需要首先建立起标准化开放接口,同时也要求我们在晶圆测试、发热管理以及新型商业模式等领域实现技术进步。

在上周召开的开放领域特定架构(ODSA)小组第二次研讨会上,我们看到了开放小芯片生态系统的稳定进展——虽然缓慢,但确实有所推进。该组织声称,目前已经有约70家成员企业正在努力为小芯片定义基于沁芯片设计的开放接口,同时亦努力建立与该堆栈相匹配的互操作小芯片市场。ODSA目前正在开放计算项目框架之下运行。

根据英特尔公司高级首席工程师兼英特尔CTO办公室制程与产品集成总监Ramune Nagisetty的介绍,芯片组的市场需求基于新兴工作负载的出现,同时亦与架构及封装技术的进步密不可分。

英特尔公司高级首席工程师兼制程与产品集成总监Ramune Nagisetty在上周的ODSA研讨会上主持了小组讨论。

Nagisetty表示,“目前行业已经发展至拐点。我们有机会通过芯片领域的创新继续实现对封装集成的扩展。”

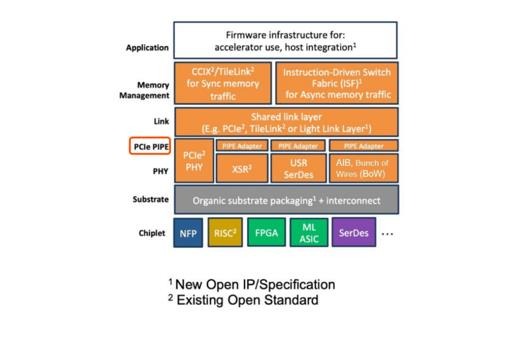

一年之前,英特尔公司为其EMIB发布了AIB协议,此项工作属于DARPA小芯片研究计划中的一部分。在上周的ODSA研讨会上,英特尔方面还推出了PHY Interface for PCI Express(PIPE)的5.2版本。其属于PCI Express接口的精简版本,据称能够实现可配置的短距离PHY。

与此同时,OSDA小组还继续努力推进自己的开放式线束(BOW)物理层接口。在ODSA研讨会上,Netronome工程师兼ODSA工作小组负责人Bapi Vinnakota积极呼吁各代工厂与芯片厂商对BOW接口提供支持;同时亦公布了一个新的小芯片设计交流项目,帮助各企业得以制定通常通过zGlue数据交换格式以机器可读形式保密的开放式小芯片物理描述。

Vinnakota指出,“对于我们这样一个开放组织,共享保密信息往往非常困难。”

BOW接口最初于今年3月的ODSA第一次研讨会上提出。BOW的基本思路在于提供一个通用且简单的并行接口,以相对较低的数据速率运行,以便将旧有节点中的芯片集成至新系统当中——例如关键性RF高级组件SiP。

虽然发展当中当然出现不少难题,但ODSA方面确实在开发开放式小芯片生态系统方面取得了稳步进展。根据Nagisetty的介绍,从外部看起来这些令人痛苦的缓慢进展,实际上体现的是其它主要技术也曾经经历过的“黎明前的黑暗”。这些发展曲线会缓慢地聚集在一起,而后逐步表现出稳定的发展加速度。

Nagisetty在接受采访时表示,“我认为在未来三到五年时间内,我们将会以一种截然不同的方式看待所有事情。进展已经出现,虽然发展速度缓慢,但其步伐将会不断加快。随着各项标准、规范以及工具的逐渐落实,变化的速度也将有所增加。我认为在三到五年的未来时间框架之内,这种基于小芯片的设计将越来越多地成为一种规则,而非特殊情况。”

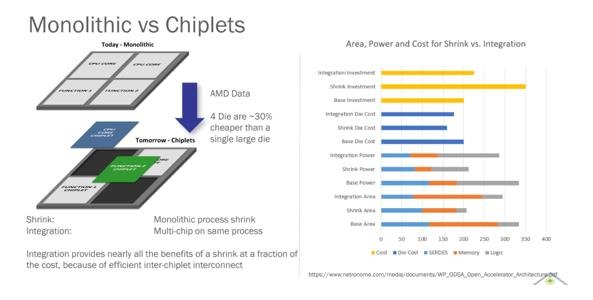

不少小芯片设计支持者经常提到的成功成本节约案例,正是AMD公司即将推出的7纳米Epyc CPU。其中包含多达8个7纳米级处理器芯片,并通过AMD的Infinity架构连接至同一14纳米I/O芯片带内存控制器。该方案是对14纳米、单封装四晶片版本Epyc的扩展。

AMD公司研究人员Gabriel Loh在出现本届ODSA研讨会时表示,“对我们来说,小芯片具有真实可信的发展前景。我们已经构建起相关实际成果,其基本思路是在芯片之上将采用不同技术节点的组件集成起来。”

ODSA研讨会上的小芯片设计经验小组。左起至右分别为:eSilicon公司Carlos Macian、AMD公司Gabriel Loh、英特尔公司Dave Kehlet、思科公司Sanjeev Joshi以及赛灵思公司Sagheer Ahmad。

然而,虽然开放式小芯片生态系统在概念上确有可行性,也已经获得了一定进展,但仍有不少批评者对此抱有怀疑,其发展道路也远非一马平川。从技术角度来看,Nagisetty认为开放式小芯片生态系统面临的最大障碍在于测试——具体来讲,即在封装之前确保芯片运作良好。这要求厂商对晶圆进行非常全面地分类,并有能力探测到各间距极小的凸点。Nagisetty同时表示,第二大挑战则在于由功率、功率密度以及热串扰所引发的发热难题。

不过从商业模式的角度来看,以上挑战只能算是开胃小菜。目前,芯片行业已经拥有与主板级组件相关的商业模式,以及与单片SoC相关的商业模式。Nagisetty表示,“但在将不同制造商的芯片加以结合方面,我们的商业模式探索之路只能算是刚刚起步。”

举例来说,SiP设备使用谁的品牌?由谁负责市场营销?另外,如果存在安全漏洞,又应该由谁来承担责任?

Loh问道,“如果产品出了问题,最后该由谁负责?”他指出,业内已经存在一些可以作为模型的解决方案,但“问题是:你要如何进行扩展?”

小组讨论期间出现的另一个问题,在于成本堆叠。如果打算全部使用来自多家芯片厂商的“同类最佳”芯片组设备,那么如果各家厂商都希望在其业界领先的芯片身上赚取高额利润,那么这些组件堆叠而成的产品将带来难以承受的价格。

Nagisetty表示,“所有这些问题都得找到对应的解决方案。所以从某种程度上讲,我们在这条道路上才刚刚起步。我们学到了很多东西,我认为这些经验最终都会通过标准与规范的形式转化为成果。”

Nagisetty指出,PHIPE规范源于英特尔的Kaby Lake G设计方案。该设计最终成就了一系列采用AMD Radeon集成图形核心的英特尔酷睿处理器,这些处理器利用PCI Express与EMIB将多个采用不同技术节点与不同制程的小芯片互连起来。

Nagisetty指出,“在这一过程中,我们逐步了解到如何将那些原本为电路板所设计的组件整合起来,并共同纳入封装之内。”

对于Kaby Lake架构,英特尔公司的设计人员最终希望利用PCI Express将CPU与Radeon GPU对接起来。然而,PCI Express在设计上主要用于调整驱动长距离信号,而且由于功率太大而无法放置在封装内部。为此,英特尔公司的设计师们提出了一种接口调整方案,用以调整信号所需要的传输距离,从而将功率降低约50%,同时亦减少了过程当中电源状态切换所需要的时间。

PIPE V5.2支持短距离应用

她表示,“我们当然也有其它办法下调功率,但如果我们能够采用PCI Express接口并控制功率,那么将能够以更低的成本创建更简单的设计方案。”由此产生的PIPE规范不仅允许设计人员在单一封装之内将互连芯片的功耗降低至合理的水平,同时也能够更灵活地设计过程后期再决定某些元件应采用板极抑或是封装级组件。

Nagisetty介绍称,除了Kaby Lake G之外,英特尔的Stratix 10 FPGA架构(通过多家代工厂在同一封装之内添加多个技术节点构建而成的芯片)以及英特尔Lakefield制程(将多个技术节点整合至同一英特尔芯片封装之内)也让芯片巨头积累起对多来源芯片进行串联的重要见解与经验。

她指出,“我们需要通过标准与规范建立起互操作性支持体系”,包括通过接口及材料规格确保在不同代工厂当中使用多种不同的兼容性材料。

好文章,需要你的鼓励

新加坡电信试点50Gbps光纤支持未来AI与云计算负载

新加坡电信启动50Gbps光纤宽带技术试点,成为新加坡首家测试该技术的运营商。该试点基于10Gbps对称无源光网络技术,旨在为未来3至5年内主流的带宽密集型应用提供基础设施支持。随着人工智能、混合现实和高保真云计算的普及,网络吞吐量和延迟性能需求将大幅提升。该举措符合新加坡数字连接蓝图规划,将支持远程办公、医疗影像传输和VR理疗等应用场景。

ETH苏黎世突破性WUSH技术:让AI大模型压缩实现接近零损失的革命性方案

瑞士ETH苏黎世联邦理工学院等机构联合开发的WUSH技术,首次从数学理论层面推导出AI大模型量化压缩的最优解。该技术能根据数据特征自适应调整压缩策略,相比传统方法减少60-70%的压缩损失,实现接近零损失的模型压缩,为大模型在普通设备上的高效部署开辟了新路径。

Pioneer发布Sphera设备为现有汽车带来高端CarPlay功能

先锋在CES 2026上发布新款Sphera车载后装接收器,首次将杜比全景声和空间音频功能引入普通汽车。该产品采用10.1英寸高清触控屏,通过"Pure Autotuning"技术优化4声道方案,充分利用现有前后扬声器。此前这些高端音频功能仅在少数特定车型中提供。Sphera售价1300美元起,将于2026年春季上市,为希望升级CarPlay的用户提供优质解决方案。

机器人终于能读懂你的手势了!弗吉尼亚大学团队让机器人变身“人类动作翻译官“

弗吉尼亚大学团队创建了Refer360数据集,这是首个大规模记录真实环境中人机多模态交互的数据库,涵盖室内外场景,包含1400万交互样本。同时开发的MuRes智能模块能让机器人像人类一样理解语言、手势和眼神的组合信息,显著提升了现有AI模型的理解准确度,为未来智能机器人的广泛应用奠定了重要基础。

Vertiv斥资10亿美元收购PurgeRite布局液冷市场

巴林如何构建区域领先的数字经济体系

阿联酋阿布扎比发布Falcon大语言模型,构建国家AI治理新模式

2025年Q3全球云基础设施支出达1026亿美元,AI应用推动增长

新加坡电信试点50Gbps光纤支持未来AI与云计算负载

Pioneer发布Sphera设备为现有汽车带来高端CarPlay功能

Twelve South推出Valet无线充电收纳托盘

苹果应该放弃自研模型,全面转向第三方AI服务

苹果设备新年优化指南:提升健康与工作效率

Thine推出iPhone智能记录应用挑战AI硬件设备

DDN表示基于Lustre的EXAScaler仍是核心产品

Unusual获得360万美元融资,专注AI模型品牌形象管理