5纳米芯片推力电池续航能力提升 原创

至顶网服务器频道 06月07日 新闻消息(文/编译):

本周一(6月5日)在东京VLSI技术与电路2017研讨会上公布的最新架构,可谓IBM公司过去十年以来同GlobalFoundries、三星以及其它多家设备供应商合作开发而成的关键性成果。根据研究人员们的介绍,相较于FinFET,这套新架构的运行功耗更低。

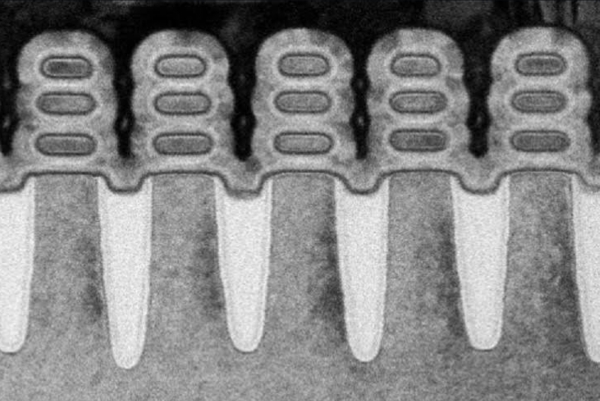

IBM/GlobalFoundries/三星共同打造的革命性5纳米纳米片晶体管,其凭借着四路多面栅能够为手机设备提到2到3天的电池续航能力。

该联盟解释称,这项革命性突破应该能够使得智能手机以及其它类似的电池供电型移动设备在一次充电后正常运行2到3天; 另外,其还能够提高人工智能(简称AI)、虚拟现实甚至是超级计算机的性能水平。

研究人员们指出,在成功开发出包含200亿个晶体管的7纳米测试芯片之后不到两年当中,他们已经在这块只有指甲大小且拥有四重多面栅的芯片中塞进多达300亿个晶体管。测试结果表明,与目前最为先进的10纳米芯片相比,其性能提升了40%(与7纳米FinFET基本相同),或者将功耗水平降低75%。

根据IBM公司的说明,这项突破性5纳米技术能够利用更为强大的性能提升认知计算能力,改善云计算与深度学习的数据吞吐量水平并帮助各类移动物联网(简称IoT)设备获得更低功耗与更高电池续航时长。

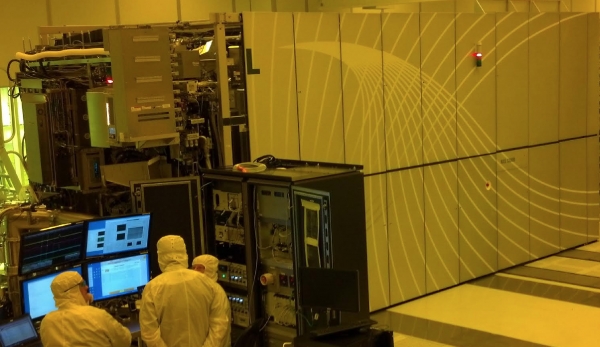

IBM公司的科学家们在位于纽约州奥尔巴尼的纽约州立大学纳米科学与纳米工程技术综合中心内对5纳米硅纳米片晶体管晶圆进行测试,旨在评估这项业界首创的制程工艺。

(图片来源: 纽约州立大学)

为了实现技术突破,该技术联盟必须克服干扰EUV(即极紫外线)光刻工艺的各类问题——事实上,此项光刻技术已经被应用于7纳米FinFET芯片的制造当中。EUV除了拥有波长较短这一优势之外,研究联盟还发现了在芯片设计与制造阶段中不断调整其纳米片宽度的办法。研究人员们表示,FinFET的性能与功率不具备微调可能性——这主要是由于FinFET受翅片高度的限制而无法增加通过电流,因此不能提供更高的性能。

科学家与工程师在位于纽约州奥尔巴尼的纳米技术综合中心之内监督EUV光刻工具在此番业界首创工艺中的实际使用,旨在确保由此构建起5纳米硅纳米片芯片。

(图片来源: 纽约州立大学)

IBM公司认为,其纳米片结构在历史地位上将等同于单单元DRAM、化学放大光电抗蚀剂、铜互连、硅绝缘体、应变材料、多核心处理器、渲染光刻、高k电介质、嵌入式DRAM、3D芯片堆叠以及气隙绝缘子等技术成果。

Globalfoundries公司首席技术官兼全球研发工作负责人Gary Patton用“开创性”来形容此项公告,并表示该公司正在积极追求5纳米以及下一代芯片制造技术。

位于纽约州奥尔巴尼的纽约州立大学纳米科学与纳米工程技术综合中心亦为IBM、GlobalFoundries以及三星的5纳米纳米片晶体管架构的研发工作作出了巨大贡献。

好文章,需要你的鼓励

AI投资有望在2026年获得真正回报的原因解析

尽管全球企业AI投资在2024年达到2523亿美元,但MIT研究显示95%的企业仍未从生成式AI投资中获得回报。专家预测2026年将成为转折点,企业将从试点阶段转向实际部署。关键在于CEO精准识别高影响领域,推进AI代理技术应用,并加强员工AI能力培训。Forrester预测30%大型企业将实施强制AI培训,而Gartner预计到2028年15%日常工作决策将由AI自主完成。

北大学者革新软件诊断方式:让代码问题的“病因“无处遁形

这项由北京大学等机构联合完成的研究,开发了名为GraphLocator的智能软件问题诊断系统,通过构建代码依赖图和因果问题图,能够像医生诊断疾病一样精确定位软件问题的根源。在三个大型数据集的测试中,该系统比现有方法平均提高了19.49%的召回率和11.89%的精确率,特别在处理复杂的跨模块问题时表现优异,为软件维护效率的提升开辟了新路径。

2026年软件定价大洗牌:IT领导者必须知道的关键变化

2026年软件行业将迎来定价模式的根本性变革,从传统按席位收费转向基于结果的付费模式。AI正在重塑整个软件经济学,企业IT预算的12-15%已投入AI领域。这一转变要求建立明确的成功衡量指标,如Zendesk以"自动化解决方案"为标准。未来将出现更精简的工程团队,80%的工程师需要为AI驱动的角色提升技能,同时需要重新设计软件开发和部署流程以适应AI优先的工作流程。

德国达姆施塔特工业大学团队首次揭秘:专家混合模型AI的“安全开关“竟然如此脆弱

这项由德国达姆施塔特工业大学领导的国际研究团队首次发现,当前最先进的专家混合模型AI系统存在严重安全漏洞。通过开发GateBreaker攻击框架,研究人员证明仅需关闭约3%的特定神经元,就能让AI的攻击成功率从7.4%暴增至64.9%。该研究揭示了专家混合模型安全机制过度集中的根本缺陷,为AI安全领域敲响了警钟。

稚晖君发布全球最小全身力控人形机器人,上纬启元开启个人机器人时代

2026年软件定价大洗牌:IT领导者必须知道的关键变化

Linux 在 2026 年将势不可挡,但一个开源传奇可能难以为继

CES 2026趋势展望:全球最大科技展五大热门话题预测

人工智能时代为何编程技能比以往更重要

AI颠覆云优先战略:混合计算成为唯一出路

谷歌发布JAX-Privacy 1.0:大规模差分隐私机器学习工具库

谷歌量子AI发布新型优化算法DQI:量子计算优化领域的重大突破

缓解电动汽车里程焦虑:简单AI模型如何预测充电桩可用性

Titans + MIRAS:让AI拥有长期记忆能力

Gemini为STOC 2026大会理论计算机科学家提供自动化反馈

夸克AI眼镜持续升级:首次OTA,支持89种语言翻译