大数据技术正全面重塑芯片方案 原创

由Amazon、谷歌以及Facebook等网络巨头所收集到的庞大数据集正带来旺盛的处理需求,这也直接推动了新一代芯片的构建。而其中两项最新成果将在今年6月下旬召开的计算机架构大会上得以亮相。

斯坦福大学的研究人员们将在会上介绍Plasticine,这款可重配置处理器能够提供近百倍于FPGA的每瓦处理性能提升,同时更易于编程。另外,由英伟达公司两位资深设计师打造的一款推理处理器则能够实现两倍于现有设备的性能与能源效率。

这些芯片的出现还仅仅是整个行业研发努力的冰山一角。英特尔公司去年收购了三家机器学习初创企业。而作为英特尔的竞争对手,三星以及戴尔-EMC亦决定注资Graphcore(来自英国布里斯托尔),后者为这一领域六家独立初创企业中的一家。

与此同时,英伟达公司亦在努力推动其GPU产品作为神经网络当中的训练平台。另外,该公司亦在积极调整具体架构以进一步提升相关工作的处理效果。

谷歌公司就此给出了不同答案——其认为无论是大规模x86 CPU集群还是英伟达的GPU都不足以最大程度完成这项任务。因此,谷歌方面推出了自己的两款加速版本,即TPU。

Graphcore公司首席执行官Nigel Toon表示,“计算2.0时代已然到来; 这显然代表着计算科学的新世界。考虑到高达98%的营收皆由搜索业务这一理想的机器学习技术应用场景所提供,谷歌公司最终使用大量由TPU构建的机架——其中几乎不存在任何CPU。”

最终,机器学习芯片将广泛出现在各类嵌入式系统当中。与全年1000万台的服务器销售量相比,目前世界范围内汽车的年销售量为1800万辆。Toon指出,“自动驾驶车辆的发展前景将给这项技术带来更为广阔的空间,更重要的是这一市场目前尚未真正建立起来。”

目前行业的普遍愿景在于开发一款AI处理器,并利用其处理当前神经网络当中的训练与推理等任务——甚至希望借此催生出部分自我学习技术。此类处理器需要以大规模并行化方式提供强大性能,但同时具备低功耗以及易于编程等优势。

事实上,连此类处理器的基本运算能力都引发了热烈的讨论。在Toon看来,此类处理器应当能够将16位浮点乘法与32位加法运算相结合,从而提供最佳精度与最低错误率。

而英伟达公司在其Volta张量计算核心当中也正是使用了这一方式,这意味着Graphcore公司将于今年10月开始向合作伙伴进行早期供应的高端芯片面临着巨大的竞争压力。这家初创企业专注于利用新型芯片内/外之内存化与互连机制构建出一款能够接入各单元与集群的大型芯片。

由Kunle Olukotun带领的斯坦福大学研究人员团队也设立起类似的目标,但采用的实现途径却与Plasticine有所不同。

“多核心时代正逐步迈向终点……在机器学习这一时代背景之下,我们需要立足于现代应用本身对计算模式加以变更,”曾率先为一家初创企业设计多核心方案(此项技术最终被引入甲骨文公司的Sparc处理器)的Oluotun解释称。

“面对机器学习中的统计模型,我们真正需要的计算方式将与经典确定性计算存在巨大区别,因此这亦代表着可观的发展机遇。”

与来自布里斯托尔的竞争对手类似,斯坦福大学的研究小组同样抛弃了共享高速缓存等传统思路。“其中最令人兴奋的因素在于硬件,大家可以对其进行重新配置以实现对特定计算任务的优化,”斯坦福大学数据科学项目执行董事Stephen Eglash在介绍Plasticine时表示。

Olukotun解释称,“我们的目标在于帮助拥有特定领域专业知识的用户在无需了解机器学习或者硬件认知的前提下构建起高质量机器学习系统。”

为了实现这一目标,斯坦福大学团队定义了Spatial,这种语言负责将算法中的各部分映射至并发处理器中的各部分。“我们立足于一套高级TensorFLow框架构建起一套完整编译器流程以表达硬件……具体来讲,其每瓦性能水平可达FPGA的10倍,而编程易行性则可达FPGA的上百倍,”Olukotun解释称。

Spatial类似于英伟达公司的Cuda GPU编程语言,但在易用性方面应该更为出色。其能够将scatter/gather或者MapReduce等函数映射至硬件当中的具体内存层级结构当中,从而实现经由DRAM与SRAM的流式数据集。

Olukotun解释称,如此一来,Pasticine处理器“即成为一个软件至上型项目”。

Eglash还意识到物联网浪潮带来的边缘计算需求必须具备对应的技术方案。“未来,我们所生产的数据量将远超面向云环境的传输能力,因此我们还需要分布式本地计算资源的协同支持。”

着眼于短期,机器学习将带来“超个性化”智能手机以自动定制用户喜好。如此一来,使用者将不再需要密码或者指纹。“手机能够在数秒钟之内即意识到当前用户是否为其真正的主人,”Eglash表示。

在工业物联网领域,推理工作已经被分配至网关处,通用电气数字公司云工程技术负责人Darren Haas解释称。“我们的一切建设项目皆可被划分为更小的设备,甚至经由Raspberry Pi单片机实现……我们将大规模模型运行在云端,并在边缘位置运行各类轻量级硬件。”

斯坦福大学构建的Plasticine是一种全新架构,并可能为Graphcore等初创企业厂商所采用。其利用并行模式与高层级抽象以捕捉具体的数据位置、内存访问模式以及控制流,从而“跨越多种不同应用密度水平”执行运算,相关论文解释称。

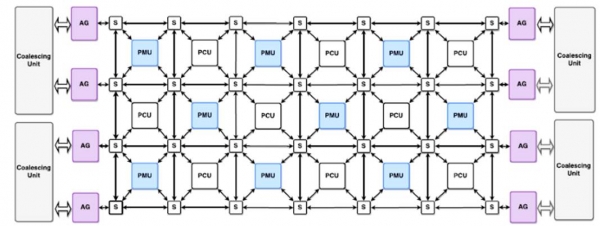

作为其核心,这款芯片采用16 x 8交错式计算单元(简称PCU)与模式内存单元(简称PMU)阵列,且各单元通过三条互连通道利用三种控制协议实现对接。这款113平方毫米的芯片采用Spatial以将应用程序映射至阵列当中,用以交付相当于28纳米制程FPGA芯片约95倍的性能水平以及高达77倍的每瓦性能。

Plasticine在1 GHz时钟频率运行状态下最高能耗为49瓦。其峰值单精度浮点运算性能为12.3万亿次,而片上总容量为16 MB。

PCU属于由执行嵌套模式之可重配置SIMD功能单元构成的多段式管道。PMU采用暂存式内存与专用寻址逻辑及地址解码器。

Plasticine采用16 x 8模式计算单元(简称PCU)与模式内存单元(简称PMU)阵列,同时内置有地址生成器与交换机制

这些主单元及其它外围元件通过字级标量、多字向量与bit级控制互连实现对接,且皆使用同样的拓扑结构。各链接采用一套分布式分层控制模式以尽可能降低需要同步的单元数量,意味着其能够实现按序、流水线或者流式执行能力。

该方案“简化了编译器的映射方式并提升了执行效率,”论文当中解释称。“每个Eplasticine组件皆用于对应用程序中的特定部分进行映射:位置地址计算由PMU完成,DRAM地址计算由DRAM地址管理单元完成,而剩余数据计算则由PCU完成。”

“从本质上讲,这可以被视为一组利用特定地址单元生成邻近地址的库式内存,”Olukotun解释称。“大家只需要提供计算布局,其即可在无需解释具体指令的前提下在正确的时间将数据导流至计算单元。”

这款芯片采用四DDR通道以对接外部DRAM,并配合缓冲与管理机制以最大程度降低芯片外处理强度。

Olukotun解释称,“目前大多数机器学习类负载专注于卷积神经网络的实现,但我们的目标是更加灵活地覆盖各类不同计算密度的算法,意味着开发者可以随时对其进行调整,从而将自己的设计思路传达给硬件。”

研究人员们还面向线性代数、机器学习、数据分析以及图形分析等常用方向构建起基准测试方案,旨在利用精确的周期对设计中的综合RTL进行模拟。“我们希望能够将这些思路贯彻到芯片方案当中,并计划在未来6到18个月之内完成芯片设计。”

Plasticine与英特尔28纳米Startix-V的性能比较结果

由九位成员组成的研究人员小组(其中七位来自英伟达公司)将出席Sparse CNN(简称SCNN)卷积神经网络推理加速器大会。该团队中包括经验丰富的微处理器设计师Joel Emer(曾协助定义并发多线程机制)以及英伟达公司首席科学家William Dally。

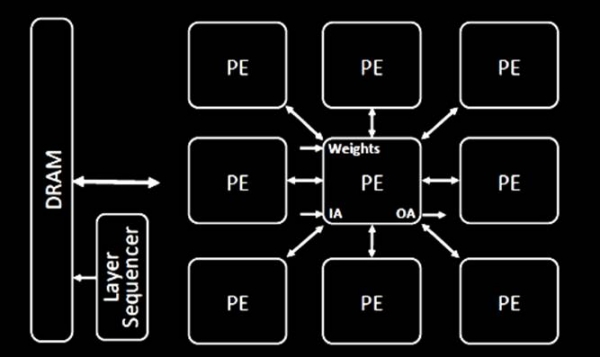

SCNN与“同等配置密度的CNN加速器”相比能够提供2.7倍性能水平以及2.3倍能源效率,论文指出。该芯片采取较此前项目更具进取性的设计思路,旨在消除无关紧要的数学运算并高度专注于处理CNN加权及其它操作。

除此之外,其“采用一种新的数据流以降低压缩编码过程中的加权与操作量,从而消除不必要的数据传输活动并降低存储资源需求,”论文同时强调称。“另外,SCNN的数据流将使这些加权与操作更加高效地被传递至乘法器阵列内,并在这里进行广泛使用。”

这套方案使得“较大CNN的所有活动始终处于片上各层间的缓冲区内,这将彻底消除跨层DRAM调用所带来的高昂网络资源需求。”

SCNN采用处理元素(简称PE)阵列以操作加权与输入/输出活动

作为核心设计概念,这款芯片中的每个处理元素(简称PE)采用一套乘法器阵列,其能够接收加权与活动向量。在采用16纳米制程技术的情况下,64个PE与16个乘数可全部被纳入1个7.4平方毫米的芯片内,这意味着其尺寸相较于同等密度的CNN加速器要略大一点。

这篇论文主要探讨了SCNN与其它研究性芯片间的差异。然而,Dally表示他认为SCNN“将凭借着低密度用例的处理优势而超越其它商用型推理加速器。”

在Plasticine方面,目前公布的结果皆立足于模拟,即尚无任何芯片制备计划。Dally指出,“我们正在进行布局设计(即布局与布线)以及时序收敛规划。”

英伟达公司并没有公布任何将此类技术进行商业化的计划,仅表示“我们仍在继续推进这方面的研究工作。”

好文章,需要你的鼓励

Locus Robotics收购Nexera Robotics,加速仓储机器人自主拣选能力升级

Locus Robotics宣布收购加拿大温哥华机器人公司Nexera Robotics,将其专有的NeuraGrasp末端执行器技术整合至Locus Array平台。NeuraGrasp融合AI抓取智能、计算机视觉及专利软膜结构,可动态适应不同形状、材质、重量的商品,显著扩大了可自主拣选的SKU类型范围。此次收购将加速Locus Robotics在移动操控领域的技术路线图,推动仓储全流程自动化履约能力迈上新台阶。

ServiceNow研究院打造“语音客服考试官“:当AI给AI打分,谁来保证公平?

ServiceNow研究团队构建的EVA-Bench框架,通过AI对AI的音频通话测试,量化评估语音客服系统在准确性和对话体验两个维度的真实表现,揭示现有系统普遍存在的可靠性缺口。

人形机器人ROI路径渐明,商业化成功关键在于有效产出

人形机器人正从原型验证迈向早期商业部署,汽车制造与物流领域预计成为未来十年核心需求市场。IDTechEx预测,相关市场规模将于2030年代初达到约250亿美元,2036年年出货量接近180万台。硬件成本持续下降,均价有望从2024年的约11.47万美元降至2030年的约3.7万美元。高利用率场景下运营成本有望低于5美元/小时,投资回收期可缩短至约6个月。但大规模商业化的关键,仍在于软件能力、任务泛化与系统集成的持续突破。

AWS AI实验室发布EvalAgent:让AI自动给AI写“成绩单“,但这件事比想象中难得多

AWS AI Labs研究团队发布EvalAgent,这是一套通过"评估技能"自动生成AI智能体评测方案的系统,将首次运行成功率从17.5%提升至65%,并在人类专家评测中获得79.5%的偏好选择。

人形机器人ROI路径渐明,商业化成功关键在于有效产出

OpenBind发布首个AI药物发现模型,推动英国领跑AI制药领域

微软新AI系统发现16个Windows漏洞,含四个高危远程代码执行漏洞

索尼发布十周年纪念款1000X Collexion旗舰耳机,搭载Edge AI技术

索尼WH-1000XM6降噪耳机推出全新砂岩配色

特斯拉将在休斯顿附近建造大型太阳能电池板工厂

Stellantis计划推出起售价低于1.8万美元的平价电动车

LiveWire收购Dust Moto,正式进军电动越野摩托车市场

Romark Logistics携手Dexory,以AI驱动实时库存可视化平台革新仓储管理

Google Workspace全面升级:新增语音、图像编辑与收件箱AI功能

暗光纤基础设施争夺战:Big Fiber获2.5亿美元融资加速AI网络布局

谷歌推出全天候 AI 智能体 Gemini Spark,助力用户高效处理日常数字任务