IBM或将推出AI加速器,期待其在实践场景下有所作为

作为早期发现加速器价值的系统设计商之一,蓝色巨人认为从长远来看,各类高性能计算都将涉及某种加速机制。换句话说,CPU应该可以把数学负载交由专用ASIC处理,由此大大缩短计算周期。

也许IBM已经从15年前的早期HPC时代汲取营养。当时的IBM曾开发出PowerXCell矢量数学加速器,并应用于洛斯阿拉莫斯国家实验室的petaflops级“Roadrunner”超级计算机。如今,这些经验教训没准也能为现代AI带来一点启发。

作为一股不一样的力量,人们当然希望IBM的加入能给AI带来新鲜的空气,至少重拾往日HPC(AI也属于HPC高性能计算中的一类)的荣光。因为有消息称,IBM研究部门似乎正在鼓捣一款新型AI加速单元。

IBM研究院的这款AIU背后还有很多细节没有披露,到目前为止,唯一能够确定的就是IBM在开发矢量和矩阵数学单元方面经验丰富,还专门发布了一篇讨论AIU的博文。

IBM研究院透露的这款AIU设备将基于5纳米工艺,而且很可能由合作伙伴三星负责制造。三星算是蓝色巨人的老朋友了,先后曾为其企业服务器制造7纳米“Cirrus”Power10服务器和面向大型机的“Telum”System z16处理器。Power10芯片就拥有非常强大的矢量和矩阵数学单元,也是IBM数十年来设计成果的演变产物。不过Telum芯片搭载的仍然是第三代AI Core混合精度矩阵数学单元,作为其片上AI推理与低精度AI训练加速器。

初代AI Core芯片发布于2018年,能够执行FP16半精度数学计算和FP32单精度累加计算,标志着IBM专门针对神经网络用例设计了低精度数据运算系统。而在为Telum z16处理器建立AI加速器之后,IBM研究院决定将这款AI加速器作为基础构建块,通过纵向扩展探索进一步发展的可能性。

在讨论新的AIU之前,我们不妨先回顾一下Telum芯片上的AI加速器。

在z16芯片上,AI加速器由128个处理器块构成,可能是4 x 4 x 8形式的2D环面配置排列,也可能是两个4 x 4 x 4物理阵列或一个4 x 4 x 8逻辑阵列,IBM并没有给出具体答案。这种脉动阵列支持FP32乘积累加浮点单元上的FP16矩阵数学(及其混合精度变体)。这样的设计能够很好地支持矩阵数学和机器学习的卷积计算,从而同时适应推理以及企业平台上常见的低精度训练需求。我们猜测,它可能还支持用于AI训练和推理的FP8四分之一精度格式,以及用于AI推理的INT2和INT4计算。我们在IBM研究院2021年1月发布的而入嵌入式/移动设备的实验性四核AI Core芯片中,就看到了这种设计。Telum CPU中的AI加速器还具有32个复变函数(CF)tile,支持FP16与FP32 SIMD指令,并针对激活函数和复变运算进行了优化。其支持的特殊函数包括:

- LSTM激活

- GRU激活

- 融合矩阵乘法,偏置运算

- 融合矩阵简洁(w/broadcast)

- 批量归一化

- Fused Convolution, Bias Add, Relu

- 融合卷积、偏置添加、Relu函数

- 最大池2D

- 平均池2D

- Softmax

- Relu

- Tanh

- Sigmoid

- Add

- Subtract

- Multiply

- Divide

- Min

- Max

- Log

一个预取器和回写单元接入z16核心和L2调整缓存环状互连,同时还接入一个暂存器,该暂存器又通过数据移动器和格式化单元接入AI核心。顾名思义,格式化单元可以格式化数据,经由矩阵数学单元运行以执行推理、产生结果。预取器则能以超过120 GB/s的速度从暂存器内读取数据,再以超80 GB/s的速度将数据存储至暂存器中;数据移动器能以600 GB/s的速度将数据取出/送入AI单元中的PT与CF核心。

在System z16大型机上,IBM能够在生产环境中支持自家Snap ML框架和微软Azure的ONNX框架,而对谷歌TensorFlow框架的支持也于两个月前进入beta公测阶段。

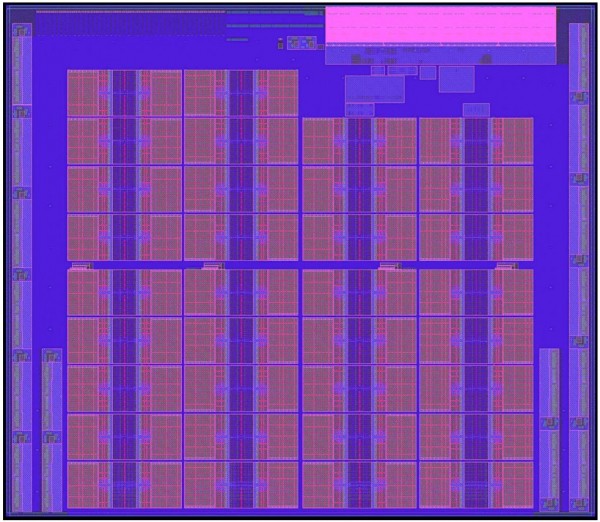

现在,假定我们将Telum芯片上的AI加速器复制出来并连续粘贴34次,就得到了下图所示的设计图:

这34个核心、用于暂存器的非核心区域,以及负责实现核心之间/核心与外部系统连通的区域,总共包含230亿个晶体管。IBM称AIU上共有32个核心,但我们可以清楚地看到34个,因此其中2个应该是为了保证设备32个可用核心所做出的冗余设计。

Telum z16处理器主频为5 GHz,但AIU不太可能以这么高的速率运行。

再来看AIU晶片,其中有16个某种类型的I/O控制器,可能是用于内存或I/O的通用串行/解串(IBM在Power10芯片I/O和内存的OpenCAPI接口中就做了这样的设计)。封装中似乎还有8组来自三星的LPDDR5内存,总内存容量为48 GB,总传输带宽约为43 GB/s。如果这些都是内存控制器,那么内存容量还有翻倍的空间,容量上限可达96 GB、传输速率上限为86 GB/s。

AIU晶片上方的控制器复合体可能是PCI-Express 4.0控制器,但我们更希望IBM能使用内置CXL协议的PCI-Express 5.0控制器。

IBM也没有透露AIU的性能表现如何,但我们不妨做一点猜测。早在2021年1月,四核AI Core芯片就已经在ISSCC芯片大会上首度亮相,其采用三星7纳米制程工艺,能够在1.6 GHz主频下提供25.6 teraflops的FP8训练性能与102.4 teraops的INT4推理性能。这款测试芯片的运行功率为48.6瓦,搭载8 MB片上缓存。

这款AIU包含34个核心,其中32个处于活动状态。因此假设时钟速率保持不变,那么其性能应该可以达到测试版本的8倍,片上缓存也同样提升至8倍。所以在片上缓存为64 MB、沿用7纳米制程、功率不超过400瓦的假设之下,其FP8精度的AI训练性能可达到204.8 teraflops,AI推理性能则可达到819.2 teraops。但IBM正考虑与三星合作引入5纳米制程,所以AIU的功率可能只在275瓦左右。

相比之下,英伟达“Hopper”GH100 GPU的PCI-Express 5.0版本功率为350瓦,可提供80 GB HBM3内存、2 TB/s内存传输带宽、支持稀疏性,能够在AI训练方面带来3.03 petaflops的性能表现。

所以IBM研究院还需要引入更多AI核心,要比现在多得多。

还有另一个问题:价格。如果英伟达给H100设定的价格在20000到30000美元之间,但IBM却能把AIU的售价控制在1000美元左右,那情况又会大不一样。虽然可能需要10个AIU才能达到H100的峰值性能(如果不使用稀疏数据,则对应5个AIU),但对于不少客户来说,AIU的成本、功率、空间和电耗毕竟只相当于H100的1/20甚至1/30,吸引力仍然非常突出。也正因为如此,英伟达才会专门推出强调AI推理场景的P4、T4和L40 GPU加速器。

好文章,需要你的鼓励

IT部门面临的十大挑战与应对策略

CIO们正面临众多复杂挑战,其多样性值得关注。除了企业安全和成本控制等传统问题,人工智能快速发展和地缘政治环境正在颠覆常规业务模式。主要挑战包括:AI技术快速演进、IT部门AI应用、AI网络攻击威胁、AIOps智能运维、快速实现价值、地缘政治影响、成本控制、人才短缺、安全风险管理以及未来准备等十个方面。

北航团队发布AnimaX:让静态3D模型瞬间“活“起来的神奇技术

北航团队发布AnimaX技术,能够根据文字描述让静态3D模型自动生成动画。该系统支持人形角色、动物、家具等各类模型,仅需6分钟即可完成高质量动画生成,效率远超传统方法。通过多视角视频-姿态联合扩散模型,AnimaX有效结合了视频AI的运动理解能力与骨骼动画的精确控制,在16万动画序列数据集上训练后展现出卓越性能。

CIO放弃散弹枪式做法,采用更具战略性的AI试点

过去两年间,许多组织启动了大量AI概念验证项目,但失败率高且投资回报率令人失望。如今出现新趋势,组织开始重新评估AI实验的撒网策略。IT观察者发现,许多组织正在减少AI概念验证项目数量,IT领导转向商业AI工具,专注于有限的战略性目标用例。专家表示,组织正从大规模实验转向更专注、结果导向的AI部署,优先考虑能深度融入运营工作流程并产生可衡量结果的少数用例。

让AI看图说话更详细更准确:上海人工智能实验室团队开发的ScaleCap技术突破

这项研究解决了AI图片描述中的两大难题:描述不平衡和内容虚构。通过创新的"侦探式追问"方法,让AI能生成更详细准确的图片描述,显著提升了多个AI系统的性能表现,为无障碍技术、教育、电商等领域带来实用价值。

IT部门面临的十大挑战与应对策略

CIO放弃散弹枪式做法,采用更具战略性的AI试点

CISO如何成为3090亿美元AI基础设施支出的守门人

PNG图像标准第三版发布,新增EXIF支持

Threads推出独立隐藏词汇管理功能并支持时限设置

论文有多水?这个AI系统一眼识破:KnoVo自动评估学术论文创新值

企业智能体扩展面临的隐形挑战与解决方案

Salesforce首席执行官:AI已承担公司近半数工作

谷歌推出AI虚拟试衣应用Doppl,让你可视化穿搭效果

超大规模运营商将在2030年前占据全球数据中心容量60%

AI初创工作室计划每年推出十万家公司

OpenDylan 2025.1版本发布:抛弃括号的Lisp语言获得重要更新