Arm如何将CHERI架构融入Morello Program硬件

芯片巨头希望调整现有处理器架构,借此消除内存访问漏洞

在本届Hot Chips大会上,Arm公司探讨了其实验性Morello Program及其CHERI架构实现原理,希望借此解决系统攻击中常被利用的一系列内存访问漏洞。

CHERI的全称,是Capability Hardware Enhanced RISC Instructions,即对能力的硬件增强RISC指令,属于英国剑桥大学与美国SRI International的合作研究项目。而Morello则是Arm将CHERI与Arm v8.2-A架构相融合所设计出的处理器原型方案。

Arm公司在今年1月发布了用于测试的Morello评估系统板,甚至还搭配一套能够在该硬件上运行的CheriBSD(基于FreeBSD)操作系统。

CHERI和Arm Morello的意义,在于调整现有处理器架构以提高系统安全性,尽可能消除内存访问所引发的各类漏洞。

根据Arm公司执行副总裁、首席架构师兼研究员Richard Grisenthwaite的介绍,目前上报的相当一部分漏洞源自缓冲区溢出或使用后释放等内存安全错误,而且这些漏洞在不同计算生态系统中往往有着广泛的“兼容性”。虽然以往业界普遍将其视为软件问题,但CHERI还是希望能从硬件出发部分加以解决。

Grisenthwaite表示,“人们已经愈发意识到,随着网络犯罪带来的损失成本日益高企,可信、可靠的安全技术方案正变得越来越重要。”

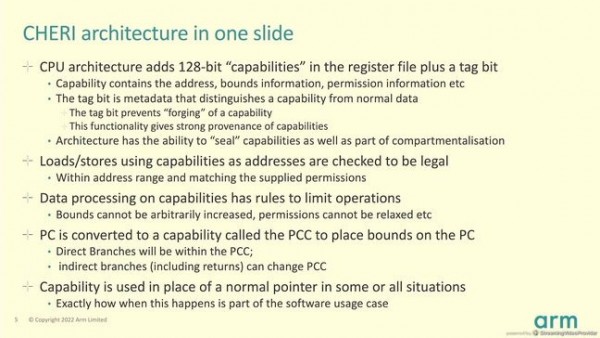

为此,Morello引入了“能力”(capabilities)这一概念,其操作类似于指针及其他数据访问寄存器。而且除地址之外,这些能力还负责存储权限和边界信息,硬件则可以使用这些信息来检查特定内存空间是否允许执行相应的代码操作。

其实能力这个概念在计算领域并不算新鲜事物,以往已经有不少大型机系统就采取过类似的机制。

Grisenthwaite解释道,“这些独立的128位单元被保存在一起,同时进一步为寄存器文件和内存系统添加元数据标签,用以将能力与数据区分开来。”这里的元数据标签非常重要,能够“帮助我们保证能力具备不可伪造的特性。”

这意味着元数据标签只能由内核或其他高权限进程所设置,攻击者只要尝试把能力当成数据来操作并更改其属性,都会导致该能力失去状态。而失去状态,也就意味着能力失效。

Grisenthwaite解释称,“最主要的变化,就是我们建立起一套完整的加载和存储体系,它们会从能力寄存器中获取自身基础地址并检查所生成的地址。这些地址通常可能会在能力范围内添加一个整数偏移量。”

对能力权限的检查会与常规内存管理检查一同进行,任何与能力检查相冲突的行为都将导致内存中止,其中止方式与转译后备缓冲器(TLB)中的内存管理故障相同。

根据Grisenthwaite的描述,Morello架构同样支持普通的加载和存储指令,这些指令会从传统的通用寄存器中获取地址。但Arm还添加了所谓默认数据能力的机制,能够为此类访问添加边界和权限,相当于为不具备能力感知的遗留代码创建起相应的沙箱。

与此同时,对能力的操作自然也需要新的数据处理指令。这些新的数据处理指令包含某些规则,允许用户在能力边界定义的范围之内执行地址调整。

Grisenthwaite还提到,“重要的是,一般来说无法在能力内添加边界。这些指令允许大家减少能力的边界或权限,通过原始对象创建子对象。但用户无法在能力不提供相应权限的前提下,扩大权限边界。”

该项目的目标之一就是调整程序计数器,将其转化为程序计数器能力,从而建立一组与之相关的边界。直接分支可以在边界之内实现分支,而间接分支则可以改变能力边界,从而在不同代码块之间实现调用。

Grisenthwaite提到,“在建立起这套功能体系之后,我们就可以用能力来全面替代以往保存在通用寄存器内的部分或全部地址,由此建立起更高的安全性基础。”

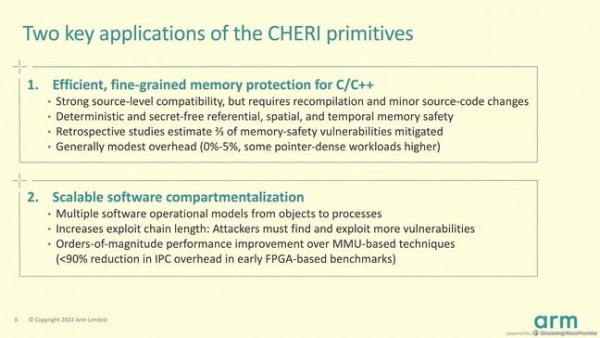

而使用这些新能力的方法之一,就是通过重新编译将程序代码中的几乎每个地址指针都替换为一项能力,这很可能需要对代码内容做出调整。根据Grisenthwaite的说法,这样能够带来更强大的内存安全性优势,通过元数据把能力跟数据区分开来,允许在C语言中释放内存时实现隔离和垃圾收集等方法。

但这套方案也有缺点,主要就是新能力会占用更大的缓存和内存。Morello原型系统中的Arm CPU内核经过定制和调整,只能支持包含一组能力的寄存器文件,而非标准的64位通用寄存器。实际上,这意味着全部寄存器都被扩展为129位,用以包含元数据标记、缓存和系统总线。

Grisenthwaite指出,在测试阶段,Arm会让所有32个CPU寄存器都可以保存数据或能力。但后续商业实施肯定会酌情削减能力寄存器的具体数量。

他解释道,“从本质上讲,已经有很多微架构扩展至129位能力,这会对整体数据路径设计产生很大影响。在Morello中,我们没有简单选择把内存中的所有数据路径宽度加倍,希望借此让处理器在性能与面积尺寸之间拥有合理的平衡点。但在生产系统中,一般会更多从性能的角度出发进行芯片设计。”

能力的存在还有助于进一步细化应用程序的划分粒度。目前的应用程序划分通常要依靠多进程来实现。

通过提供更细粒度的划分,即可限制单一漏洞利用可能造成的危害,在提高软件健壮性的同时增强系统的整体安全性。

而另外一个优势是,与传统的进程切换相比,CHERI架构还能够将把不同划分间的切换成本降低几个数量级。

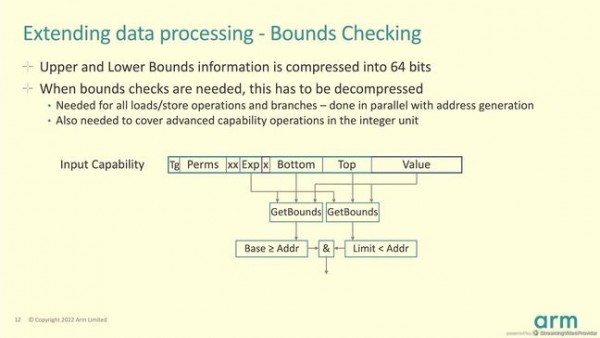

CHERI中还有一种非常有趣的实现方式,也就是把能力的边界和权限信息以压缩格式加以存储,因此只需要添加额外的64位状态信息。但这也意味着在执行地址检查时,基址和边界值需要经过解压,之后才能跟地址计算结果进行比较。

根据Grisenthwaite的介绍,他们在压缩方面投入了大量精力,希望提出一种随时能够快速解压的方案,以免影响设备上的其他关键部件。

“在内存访问路径当中,基址和边界的解压缩会作为地址生成算法的并行扩展同步完成。这意味着边界检查的耗时,与正常的TLB命中非常相似。”

至于对软件的影响,Grisenthwaite表示,CheriBSD中基于X11 KDE的桌面环境是由一位工程师耗时三个月移植到Morello的,全程只对全部600万行代码中的不到0.03%进行了更改。而小小的变化,让系统脆弱性和漏洞缓解率提升了约73.8%。

微软安全研究中心(MSRC)发布的一项详尽研究,也证实了Arm对于Morello的安全信心。研究中心调查了2019年影响微软产品并需要更新修复的所有内存安全漏洞,并得出结论称,配合其他处理措施,CHERI至少可以缓解其中三分之二的安全问题。

由于目前尚处于纯原型设计阶段,还不属于商业产品,因此Arm只制造了少量Morello系统板。在英国研究与创新(UKRI)组织的指导下,Arm开始将Morello交付给各家合作伙伴,包括谷歌、微软以及其他高校和企业。

但CHERI并没有申请技术专利,Arm也鼓励计算行业内的其他各方开展评估,同时将Morello作为技术展示架构。

Grisenthwaite总结道,“我们对这项技术的前景万分期待,也希望看到Morello将以怎样的方式开拓出这条大有可为的安全改善道路。”

好文章,需要你的鼓励

Nextdoor推出AI推荐功能重新设计应用界面

邻里社交应用Nextdoor推出重新设计版本,新增本地新闻、实时警报和名为"Faves"的AI功能,用于发现本地商户和地点。该应用与3500家本地出版商合作提供新闻内容,通过Samdesk和Weather.com提供天气、交通、停电等实时警报。Faves功能利用15年邻里对话数据训练的大语言模型,为用户提供本地化AI推荐服务,帮助用户找到最佳餐厅、徒步地点等本地信息。

Skywork AI的多模态推理新突破:让AI像人类一样“慢慢思考“解决复杂问题

Skywork AI推出的第二代多模态推理模型R1V2,通过创新的混合强化学习方法,成功解决了AI"慢思考"策略在视觉推理中的挑战。该模型在保持强大推理能力的同时有效控制视觉幻觉,在多项权威测试中超越同类开源模型,某些指标甚至媲美商业产品,为开源AI发展树立了新标杆。

英国生物银行完成NHS全身成像项目创纪录成就

英国生物银行完成了世界上最大规模的全身成像项目,收集了10万名志愿者的超过10亿次扫描数据,用于研究人体衰老和疾病过程。该项目历时11年,每次扫描耗时5小时,投资6200万英镑。目前已有8万人的成像数据供全球研究人员使用,剩余数据将于年底前发布。项目已开发出能预测38种常见疾病的AI工具,并在心脏病、痴呆症和癌症诊断方面取得突破。

北京大学团队首次全面评估GPT-4o图像生成能力:AI绘画竞赛中的新冠军诞生

这项由北京大学等多所高校联合完成的研究,首次对OpenAI GPT-4o的图像生成能力进行了全面评估。研究团队设计了名为GPT-ImgEval的综合测试体系,从文本转图像、图像编辑和知识驱动创作三个维度评估GPT-4o,发现其在所有测试中都显著超越现有方法。研究还通过技术分析推断GPT-4o采用了自回归与扩散相结合的混合架构,并发现其生成图像仍可被现有检测工具有效识别,为AI图像生成领域提供了重要的评估基准和技术洞察。

Nextdoor推出AI推荐功能重新设计应用界面

英国生物银行完成NHS全身成像项目创纪录成就

关税凸显了韧性供应链的必要性

学霸还是学渣,数学能力训练到底提升了什么?深度揭秘大模型能力迁移的秘密

首款推理型智能体来了!微软研究助手+分析助手,帮你更聪明地工作

F5推出后量子密码学解决方案,助力企业应对新一代安全威胁

大胆撞色点燃夏日灵感,西部数据推出极客(TM) G-DRIVE(TM) ArmorATD(TM) Apple独家新配色

AI应用的“安全锁”:安全闪存技术在满足行业认证中的作用

黄仁勋:H20 将在中国恢复销售,并针对中国推出全新且完全兼容的专用 GPU

Meta建设5GW超大规模AI数据中心抢占AI竞赛先机

Google为NotebookLM添加精选笔记本功能,涵盖多元化主题内容

Claude AI 现已集成 Canva 设计平台