运用GPU加速芯片设计,借力AI推动芯片发展

二十年前,包括英特尔在内的所有芯片制造商在芯片的自动化设计和测试方面只有一个选择——Unix设备,而且大多是Sparc/Solaris系统。英特尔一直心心念念想要夺取这块服务器业务,再加上Linux当时风头正劲,自然希望能把电子设计自动化(EDA)转移到x86平台之上。

但Synopsys、Cadence、Mentor Graphics等EDA厂商根本不打算真出什么力气,于是为了自身更大的利益,英特尔决定开明一把、帮助他们将EDA工具全部移植到x86架构的Linux平台。这是一项巨大的工程,但也切实降低了设计成本、增强了可扩展性,最终让芯片巨头在降低数据中心内外计算成本方面取得了巨大成功。

如今,新一轮芯片设计变革似乎即将到来,而此次颠覆一切的核心要素正是人工智能(AI)。

就在不久之前,整个半导体行业还在遵循摩尔定律提出的发展规律,似乎没人想过这条定律还能持续多久。从45纳米到32纳米,再到后来的28纳米、22纳米、16/14纳米,直到最近的10纳米和7纳米,虽然发展的道路从不平坦,但才华横溢的从业者们总能找到突破之法。

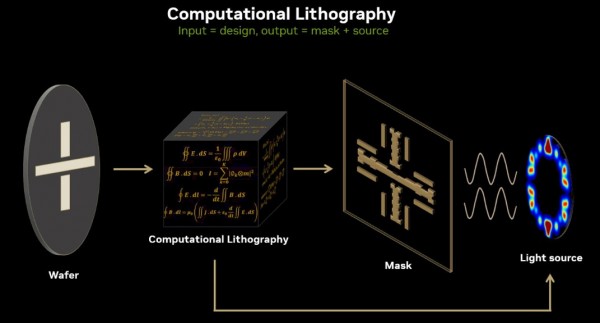

如今,英特尔、AMD等厂商开始冲击摩尔定律最后的堡垒——5纳米、3纳米,乃至于2纳米甚至1.8纳米的更小晶体管结构。在这样的尺寸下,传统制程工艺已经没有任何参考价值,半导体厂商开始转向计算光刻——即凭借算法在晶圆上规划元件、模拟生产流程并创建出可用于实际制造的掩膜。英伟达公司创始人兼CEO黄仁勋在最近的GPU技术大会上,就将这个挑战总结成“物理极限下的成像问题”。

英伟达高级技术集团副总裁Vivek Singh在线上会议中,这样向记者和分析师描述英伟达GPU的加速光刻技术:“每种芯片设计方案都由约100层构成,其中总计包含数万亿个多边形或者图案。其中每一层都被单独编码成一个光掩膜,也就是用于设计的模板,并使用极为昂贵的光刻机将其依次印刷在芯片上。由此得到的由晶体管和线路组成的三维结构,也就是大家使用的芯片。”

Singh还补充称,大约30年前,“构成芯片的晶体管和导线已经缩小到比光刻机中的激光器还小,由此产生的衍射现象令晶体管的图案变得模糊。如果不加以解决,这些图案会越来越模糊,无法实现正确印刷。必须采取一些措施来解决所谓波长差距,而答案正是计算光刻。”

所有这一切都指向对计算能力的需求。更小的晶体管意味着更复杂的计算任务,对数据中心来说,这代表着必须使用更多专门用于计算光刻操作的服务器。Singh表示,这类数据中心的规模增长速度快摩尔定律更快。因此到本世纪末,目前只需3处数据中心的晶圆代工厂将需要100处数据中心才够用。“过去15年的经验恐怕只能再支持几年了,后面还是得想新办法。”

人们一直在努力创建工具,希望能降低计算光刻门槛,借此保持高效、快速且具有成本效益的芯片制造能力。正如英特尔早先在x86架构身上投入的心力,英伟达如今也打算用同样开明的态度完成这波变革——只是这一次要操作的不是可见光,而是极紫外线。在最近的GTC 2023大会上,英伟达公布了cuLitho,这是一套计算光刻软件库,将运行在由该公司“Hopper”H100 GPU加速器提供支持的DGX H100超级计算机之上。

自从十多年前将GPU加速器引入数据中心以来,英伟达对cuLitho的思路定位就从业没有改变过——将高度并行处理的工作负载(比如计算光刻)从CPU转移至GPU,将大大提高性能水平和执行效率。

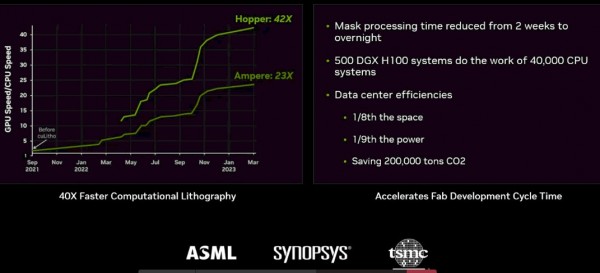

英伟达表示,cuLitho、DGX系统和Hopper GPU的组合有望以极低的功率实现40倍以上的性能提升——由CPU系统构成的数据中心总功率如果是35兆瓦,那么英伟达芯片支持的数据中心则仅为5兆瓦。利用cuLitho,晶圆代工厂能够产出3到5倍以上的光掩膜,且功耗仅为当前水平的九分之一。据英伟达介绍,以往需要两周才能完成的光掩膜制造如今能在一夜之间搞定。计算结果还显示,由4000个H100 GPU构建并配合cuLitho运行计算光刻作业的500个DGX系统,其性能已经可以与40000个CPU支持的系统相当,而功耗仅为后者的七分之一。

cuLitho库也将能够在旧有英伟达GPU架构上运行,例如Volta和Ampere,但英伟达建议新用户尽量直上Hopper。

英伟达还在积极拉拢行业内的团结力量。台积电正在将cLitho整合至自家代工业务当中,光刻设备制造商ASML把GPU支持集成至其计算光刻软件产品内,而EDA厂商 Synopsys则着手将cuLitho纳入自家软件和系统。

话虽如此,英伟达目前并未透露关于cuLitho的更多细节,包括商业模式。所以尚不清楚英伟达打算向EDA厂商还是客户开放许可。Singh也把话题引向了AI和cuLitho上面,对具体使用的算法并没有多聊。但他同时提到,“AI在cuLitho中发挥着重要作用。相较于基于CPU的系统,我们实现了42倍的性能提升。希望未来能在AI的帮助下进一步增强系统性能。”

这也在情理之中。AI正迅速渗透至半导体设计布局的方方面面。英伟达上个月刚刚展示如何使用其四年前打造的DREAMPlace GPU来加速深度学习工具包,从而确定内存等晶体管组件、PCI-Express控制器/内存控制器等模拟设备,乃至核心本身在半导体设备上的放置点位,借此实现由手动到自动的全面提速。

Synopsys也通过其EDA工具全力押注AI技术。2020年,该公司朝这个方向迈出了第一步,发布DSO.ai。这是一款包含AI技术的芯片设计应用程序,并在今年早些时候达到了流片生产1000次的里程碑。三星和Microelectronics等公司都是DSO.ai的用户,Synopsys希望借这款工具在芯片设计的各个步骤中测试AI的可行性。Synopsys EDA集团产品线管理高级总监Arvind Narayanan表示,DSO.ai已经成为该公司重要的技术试验场。

Narayanan在采访中表示,“要如何有效使用AI建立模型,从而以远超人类的速度将制程缩小到全球领先的水平?我们也是第一次尝试回答这个问题,并从中学到了很多东西。”

最初,组织主要利用这款工具优化半导体设计中的功率、性能和面积(PPA)指标。但在此之后,设计人员扩大了用途,包括确定流程规划中的最佳配置和加快不同设计方案之间的迁移。

在上月底举行的Synopsys User Group(SNUG)活动中,该公司发布了Synopsys.ai,基本上就是将AI和机器学习技术应用在EDA流程中的各个环节。新方案具体分为三个类别:负责设计空间优化的DSO.ai、负责验证空间优化的VSO.ai,还有负责测试空间优化的TSO.ai。其全面覆盖了从芯片制造到实现、再到系统架构的各个方面,其中大部分功能都来自Synopsys公司通过DSO.ai积累到的知识。

Narayanan表示,“一旦接触过AI实现,就能体会到它在生产力和PPA角度带来了诸多助益。而接下来要解决的问题,就是要如何逐步扩展它的功能效用。既然AI在实现层面有所建树,那它能不能搞定验证、测试和确认呢?这些又各自对应很多流程。另外就是,怎样使用AI构建出的模型?怎样共享这些模型并有效运用?随着探索和前进,连客户都开始询问我们,为什么只尝试用AI解决如此有限的问题。没错,我们确实应该持续扩张、努力突破应用边界。”

与英伟达为cuLitho制定的策略一样,Synopsys.ai的存在意义,也是为了解决制程工艺越来越小、芯片制造从2D转向2.5D乃至3D所带来的极高复杂度难题。此外,美国政府和环保机构也在向芯片制造商和其他数据中心相关方施压,要求他们想办法降低此类大型基础设施所消耗的电力。

驱动AI设计的最后一点,在于半导体设计领域长期缺乏可用人才。而AI的协助不仅有望实现流程自动化,也能降低半导体行业的从业门槛。

“AI也许会在这个关键领域提供重大帮助。目前整个半导体行业都在寻求颠覆性的方案,协助解决愈发严重的人才短缺问题。企业确实很难找到劳动力满足生产方面的需求。而且随着芯片项目周期变得越来越短,芯片厂商必须保证在特定期限之前将产品投放市场,这样才能保持良好竞争力。我们正在见证这一巨大转变,也坚信作为一种颠覆性技术,AI必将帮助设计师达成这样的生产力目标。”

Synopsys对DSO.ai和现在Synopsys.ai整体堆栈的悉心打造,也切实为其带来了相较于Cadence等竞争对手的先发优势。

好文章,需要你的鼓励

CES上杨元庆首谈AGI,碾压人类的叙事不会让AI更聪明

很多人担心被AI取代,陷入无意义感。按照杨元庆的思路,其实无论是模型的打造者,还是模型的使用者,都不该把AI放在人的对立面。

MIT递归语言模型:突破AI上下文限制的新方法

MIT研究团队提出递归语言模型(RLM),通过将长文本存储在外部编程环境中,让AI能够编写代码来探索和分解文本,并递归调用自身处理子任务。该方法成功处理了比传统模型大两个数量级的文本长度,在多项长文本任务上显著优于现有方法,同时保持了相当的成本效率,为AI处理超长文本提供了全新解决方案。

Gmail新增Gemini驱动AI功能,智能优先级和摘要来袭

谷歌宣布对Gmail进行重大升级,全面集成Gemini AI功能,将其转变为"个人主动式收件箱助手"。新功能包括AI收件箱视图,可按优先级自动分组邮件;"帮我快速了解"功能提供邮件活动摘要;扩展"帮我写邮件"工具至所有用户;支持复杂问题查询如"我的航班何时降落"。部分功能免费提供,高级功能需付费订阅。谷歌强调用户数据安全,邮件内容不会用于训练公共AI模型。

华为研究团队突破代码修复瓶颈,8B模型击败32B巨型对手!

华为研究团队推出SWE-Lego框架,通过混合数据集、改进监督学习和测试时扩展三大创新,让8B参数AI模型在代码自动修复任务上击败32B对手。该系统在SWE-bench Verified测试中达到42.2%成功率,加上扩展技术后提升至49.6%,证明了精巧方法设计胜过简单规模扩展的技术理念。

联想集团混合式AI实践获权威肯定,CES期间获评“全球科技引领企业”

CES上杨元庆首谈AGI,碾压人类的叙事不会让AI更聪明

CES 2026 | 重大更新:NVIDIA DGX Spark开启“云边端”模式

Gmail新增Gemini驱动AI功能,智能优先级和摘要来袭

研究发现商业AI模型可完整还原《哈利·波特》原著内容

Razer在2026年CES展会推出全息AI伴侣项目

CES 2026:英伟达新架构亮相,AMD发布新芯片,Razer推出AI奇异产品

通过舞蹈认识LimX Dynamics的人形机器人Oli

谷歌为Gmail搜索引入AI概览功能并推出实验性AI智能收件箱

DuRoBo Krono:搭载AI助手的智能手机尺寸电子阅读器

OpenAI推出ChatGPT Health医疗问答功能

Anthropic寻求3500亿美元估值融资100亿美元