ARM再出手,充实服务器芯片路线图中的空白与细节

文章开篇,我们不妨先回顾历史:开发Arm服务器芯片的第一波尝试,包括Calxeda、Applied Micro、AMD、Marvell、英伟达以及三星等,已经彻底失败。第二波浪潮同样折戟沉沙,博通、Cavium、高能和Nuvia纷纷在此饮恨。但后继者们仍未停下探索的脚步。

在第三波Arm服务器芯片研发浪潮中,超大规模厂商、云服务商(包括亚马逊云科技、微软、谷歌、阿里巴巴和腾讯)以及部分独立芯片设计商(主要有Ampere Computing、HiSilicon、英伟达和SiPearl)纷纷与Arm公司合作。看起来,这场围绕Arm架构展开的服务器芯片远征还将持续下去。

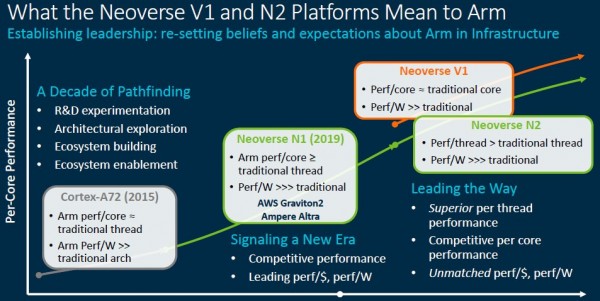

毫无疑问,Arm阵营之所以能吸引到各方前赴后继的加入,依靠的就是Arm公司在2018年10月公布的将消费级芯片设计与服务器业务彼此拆分的战略。Neoverse从零开始设计Arm核心,使其具备了承接服务器工作负载所必需的功能、L2缓存、网状互连和更强大的晶体管。基于各项要素共同形成的核心复合体,Neoverse参考架构允许芯片设计师们灵活接入自己选定的DDR内存、PCI-Express外设和网络接口控制器,在很大程度上降低了服务器芯片的自主设计风险。也就是说,只要持有Arm架构许可证,各厂商就可以自由选择要不要根据Neoverse的参考方案开发自己的定制化Arm核心。

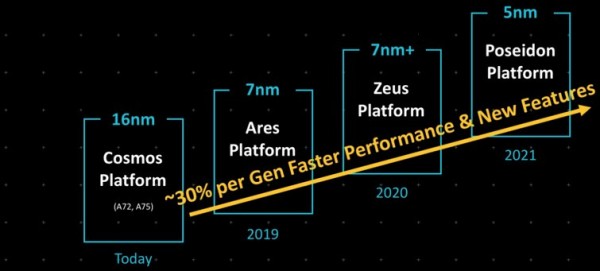

当时,Neoverse对自家参考平台做出承诺,称将每年开发出一套新的Arm服务器平台,且每次升级至少将性能提升30%。

这份路线图堪称简单粗暴中的典范。他们计划开发出基于Arm架构的CPU,将核心数量设定在4个到128个的广泛区间,内存带宽也从GB级别支持到TB级别,用以满足从边缘场景到云端数据中心的各类计算需求。

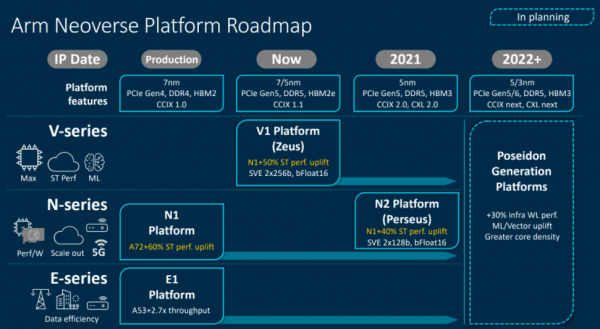

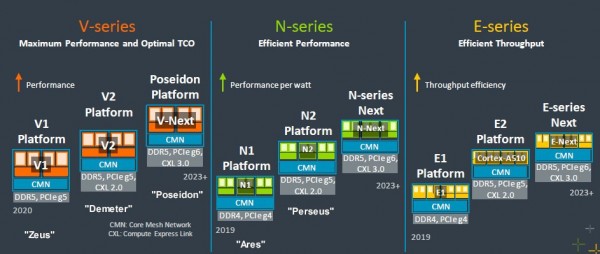

Neoverse路线图在2020年9月迎来一波更全面的扩展和充实,首次划分出V系列(强调用于浮点计算的胖向量)、N系列(具有高吞吐量整数性能)和E系列(为适度计算需求提供更好的能源效率):

2021年4月,Arm又披露了其服务器CPU三大分支系列的更多细节:

这里又具体涉及“Zeus”Neoverse V1和“Perseus”N2核心的架构区别。受篇幅所限,本文不做过多展开。

总之,我们认为V系列核心应该是在2019年末到2020年初之间匆忙提出的Arm许可核心,主要面向超大规模厂商和云服务商(特别是拥有多处高性能计算中心的服务商),强调在整数和浮点数方面提供更强性能。

而随着高端V系列和低端E系列的加入,Arm的工作量开始快速增长,已经无法保持当初Neoverse提出的每年更新的目标。因此,原本预计于2021年发布的“Poseidon”系列芯片要到2023年及之后才会亮相。这其实不是坏事,毕竟市场还没准备好迎接这么频繁的处理器升级。Neoverse N1核心得先做好精兵简政,并在一定规模之内证明自己的生产能力,之后才能说服整个市场相信Neoverse可以提供稳定可靠的商用芯片。

如今,第一阶段目标已经达成。接下来,Arm可以用更多核心变体来充实这份Neoverse路线图,让公众了解接下来有哪些新成果值得期待。

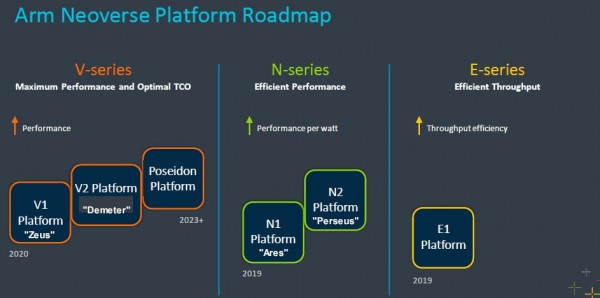

下面来看刚刚更新的Neoverse宏观路线图:

我们在图中标出了已知的核心代号,这样可能更便于区分。

本轮新增的核心是“Demeter”V2核心。虽然相关消息不多,但据我们了解,它是英伟达决定在其“Grace”Arm服务器CPU中使用的核心,相关产品预计将从明年开始发货。英伟达已经在上个月的Hot Chips 34大会上确认了这方面消息。之前,英伟达一直对Grace系统要使用哪款核心三缄其口,所以很多人怀疑图形芯片巨头肯定是要用自研核心。毕竟2011年1月时,英伟达就曾经计划在后续产品线中使用“Denver”Arm服务器CPU,只是因为一系列复杂原因而未能实现。

但即使这次选择了Arm的现成方案,也不代表英伟达后续不会再次自行研发定制化核心。Ampere Computing已经在使用N1核心,但没有停止为后续芯片开发自主核心的步伐。AWS在Graviton 1中使用的是半定制“Maya”Cortex-A72核心,在Graviton 2中转向了N1核心,并计划在新的Graviton 3中使用V1核心。

Arm已经在Neoverse这个台子上唱起三出戏,对应三套不同核心。但为什么其他芯片设计商愿意走上台来,接着Arm的参考架构开发自己的核心方案?

Arm公司基础设施产品解决方案副总裁Dermot O’Driscoll在采访中表示,“Arm生态系统的美妙之处,在于我们提供出色的灵活性。有些合作伙伴希望充分发挥这种灵活性,进而设计出自己的核心。由此带来的成果,就是他们打造出的Arm异构产品。我们当然坚信Neoverse在市场上的强大竞争力,但也相信合作伙伴能够为市场带来更多引人注目、有趣有效的解决方案。Arm生态系统的美妙之处,就在于提供丰富的选项。大家知道,还有很多生态并不提供类似的灵活选项。”

对,完全不提供。

无论如何,“Poseidon”已经不再是独立的产品系列,而是转化为下一代V3核心和围绕它建立的相关平台。

下面来看一份更完整的路线图,其中展示了第三代V、N和E系列核心的设计目标:

我们同样在图中添加了可以确定的代号,这样应该能让冷冰冰的型号变得更上口。

首先,下一代V3、N3和E3的代号还不确定。我不太清楚Arm为什么不赶紧给它起个名字,毕竟这样更有利于传播。当然,这只是小事,更重要的是Arm各合作伙伴接下来可以通过许可IP开发自己的服务器CPU。事实上,我们预计中国也会有不少厂商加入进来。毕竟英伟达没能成功收购Arm,美国政府主导不了这项交易,就连愿意出场一切来换取贸易平衡的英国也不想将Arm拱手让给中国。总之,事情已经僵在现在这个状态下了。

在各个Arm核心系列当中,都能看到配套的相干网状网络(CMN)。它的作用是将各个核心彼此连接,再接入CPU上的L2缓存和其他控制器/接口。

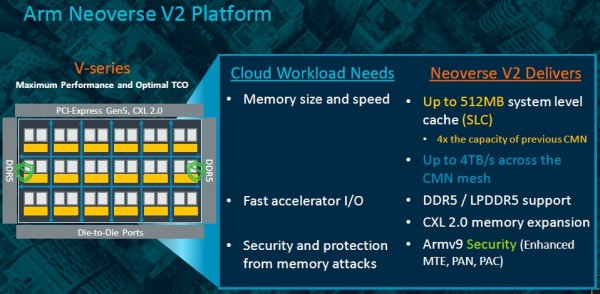

Demeter V2核心配备的是DDR5内存和PCI-Express 5.0外设控制器,并将支持用于加速器的CXL 2.0相干内存协议,因此可以跨服务器建立内存池。V2核心肯定会支持2021年3月发布预览的Armv9-A架构,其中包括支持第二代可扩展向量扩展(SVE2)微量数学设计——该设计将四个128位向量捆绑在一起,可支持INT8和BF16格式,以及常规的单精度FP32和双精度FP64浮点数学运算。

因此,基本可以断定Grace将是首款搭载SVE2引擎的商用产品。此举出自英伟达之手也绝非偶然。另外,我们还预计将在re: Invent 2022大会上看到采用V2核心的Graviton 4芯片预览版。现在看起来,SVE2的市场首秀应该就是AWS和英伟达之间的速度竞赛了,不知道谁能抢先一步。

超大规模厂商和云服务商也在积极推广Ampere Computing A1核心,即该公司定名为AmpereOne的定制化核心。与此同时,各大厂商似乎也在推动其他Arm V2核心设计方案:

V2核心采用64位虚拟内存寻址与48位物理寻址,因此单插槽核心复合体能够对接最高256 TB的物理内存。对于传统CPU用例来说,这样的内存容易似乎已经绰绰有余。但对于IBM家的Power10芯片这类支持巨大共享内存池的用例,其单服务器物理内存支持上限已经来到了2 PB。看似疯狂,但蓝色巨人这么做有其深意。用户可以将其视为共享内存区域网络,并通过Power10提供的高速NUMA互连轻松实现。

V2核心将搭载64 KB指令L1缓存,64 KB具有新增纠错功能的L1数据缓存,并提供将L2缓存容量从V1核心的1 MB提升至2 MB的选项。Arm公司承诺达成“市场领先的整数计算性能”,虽没有具体说明,但我们已经看到了Grace的SPEC整数速率性能指标。在SPECint_rate_2017吞吐量测试中,72活动核心的成绩非常不错,得分约为370。

V2核心的配套CMN网格最多可跨256个核心,因此总L2缓存容量可达512 MB。这一核心数量达到V1的2倍,L2内存则达4倍。当然,考虑到CMN网格高达4 TB/秒的总带宽,提升指标也完全合理。V2平台支持DDR5和低功耗DDR5(LPDDR5)主内存,后者已经被英伟达指定为Grace CPU的主内存。V2平台还支持PCI-Express 5.0外设,可运行CXL 2.0内存池协议,但用户需要等待PCI-Express 6.0和CXL 3.0协议落地后,才能通过PCI-Express对接入CPU的共享内存进行切换。

我们再对下一代Poseidon V核心做一点展望。这里暂时将其称为“Poseidon”V3核心,跟前面的其他名称保持一致。预计这款V3将于明年正式发布,目前已知的消息就是支持DDR5内存、PCI-Express 6.0外设和CXL 3.0协议。

Perseus N2核心的消息也不多,应该是跟V2核心一样遵循ARMv9-A规范。目前的普遍共识是,Arm应该只会对N2核心的每瓦性能做一点优化设计,毕竟以超大规模厂商和云服务为代表的用户们看重的就是这个。使用N2核心的CPU主要集中在12核到36核、功率在30瓦到80瓦之间。结合之前得到的消息,我们认为V1核心在超大规模厂商和云服务商群体内空间不大,但在高性能计算系统中有望受到欢迎。另外,AI推理已经成为CPU设计中的重要因素,所以N2核心基本也就告别了数据中心场景,这部分市场应该主要是V1和V2的天下。照常理来看,N2核心应该主要用于5G、其他网络场景以及DPU。但这部分市场肯定还要被2021年初推出的E系列拿下一部分,后者毕竟是专门针对每瓦性能设计的产品。

再有,我们还听说N的下一代芯片会被命名为“Triton”或者“Orion”,用的是神话中Poseidon儿子的名字。不知道Arm为什么不直接在路线图上称其为N3核心,总之其在设计上仍将沿用DDR5、PCI-Express 6.0和CXL 3.0的功能集组合。

作为有可能在5G和部分网络应用场景中抢N系列饭碗的产品,Arm为E系列选择了Cortex-A510核心,也就是Cortex A55的继任者,主要面向智能手表、各种消费级设备和智能手机等。由此设计出的E系列服务器核心和平台,将与V2和N2拥有相同的内存和I/O支持能力,而且肯定会支持Armv9-A架构。另外我们还了解到,下一代E核心及平台将于2023年及之后推出,同样全面匹配Neoverse V3和N3的设计思路。

好文章,需要你的鼓励

谷歌Project Genie新增街景功能,带你探索真实世界

谷歌宣布为旗下互动世界构建工具Project Genie新增Google街景功能,用户可基于真实地点生成可探索的游戏世界。只需选定美国境内的地图位置,描述角色形象,并选择"沙漠"或"石器时代"等风格,系统即可生成与现实街景绑定的沉浸式虚拟场景。每次游玩时长限60秒,支持WASD操控,目前仅向AI Ultra订阅用户开放,后续将逐步扩展覆盖范围。

新加坡国立大学发布首个视频“潜台词“理解基准测试:AI究竟能不能读懂视频背后的弦外之音?

新加坡国立大学构建了首个视频隐喻理解基准ViMU,含588段视频与2352道题,测试16个主流AI模型均未超过50%,揭示AI在视频潜台词理解上的系统性短板。

手机上的“氛围编程“时代正式来临

随着AI编程工具的普及,越来越多的非开发者开始尝试自己构建应用。谷歌在I/O大会上宣布,AI Studio新增功能可让用户通过提示词快速生成原生Android应用,并直接导出到手机。此外,谷歌还推出了基于Gemini的自定义小组件功能,并提出"生成式UI"概念,让手机界面根据需求实时生成。与此同时,苹果据报道也在探索通过提示词创建快捷指令的功能,手机个性化体验或将迎来新突破。

浙江大学联合多所顶校:让AI真正“看懂“360度全景图,机器人导航和视觉搜索迎来新突破

浙江大学等机构联合提出PanoWorld,通过球面空间交叉注意力和57万张全景图训练数据,让AI能直接理解360度全景图的空间结构,在导航和视觉搜索任务中大幅超越现有方法。