怪兽级芯片的时代正在来临

哪些系统设计要求SoC复杂性进行飞跃式发展?正确答案绝不仅仅是大家首先想到的大数据中心人工智能(AI)芯片,同时还包括无人驾驶汽车等场景,例如汽车、卡车以及无人机。此外,能够自主着陆的可重复利用火箭,以及可以进行远程诊断的医疗设备,也都是这类芯片的需求主力。

目前,很多片上系统(SoC)的设计复杂性已经令人难以想象。例如,今年HotChips研讨会上展示的针对边缘与数据中心等场景的各类全新SoC设计,就令人大开眼界,甚至进一步拓展了我们对于“大”芯片的定义范围。那么,到底哪些系统设计要求SoC复杂性进行飞跃式发展?正确答案绝不仅仅是大家首先想到的大数据中心人工智能(AI)芯片,同时还包括无人驾驶汽车等场景,例如汽车、卡车以及无人机。此外,能够自主着陆的可重复利用火箭,可以进行远程诊断的医疗设备,以及用于支持智能制造的联网机床控制器,也都是这类芯片的需求主力。

凭借着夸张的尺寸与复杂性,这些芯片开始被人们称为“怪兽级芯片”。在今天的文章中,我们将共同了解这些怪异芯片设计方案兴起背后的驱动因素。简而言之,此类特殊设计主要是为了实现互联网连接,这种连接能力不仅可以带来大数据信息,同时还能实现有助于决策的分布式处理机制。这些与互联网连接的系统,往往需要通过每秒处理超过万亿次运算的方式自行做出一部分甚至所有决策,而这也进一步推动了又一轮硬件与软件创新热潮,并最终令芯片的复杂度迈向前所未有的高度。

图一:无人驾驶、机器学习以及区块链处理等场景对复杂性的严苛要求,带来了新一代SoC设计方案。

没错,也有一部分应用仅负责信息报告,但这类应用通常数量非常有限,而且代表着低价值市场上只能产生较低利润率的产品门类。为了真正实现价值,联网系统必须有能力自主做出决策,而这就带来了独特的软件与硬件开发挑战。

首先,为了能够做出决策,这些系统需要建立起一整套包含多种类型传感器,以及由复杂软件算法驱动的高性能数据处理体系。可以肯定的是,硬件由软件需求进行驱动,而设备本身也需要支持能够使系统与现实世界进行交互的其它算法。

没错,大家可以在软件与硬件之间旋转几个中间件层,但这会牺牲性能表现,并给多种关键任务应用带来额外的执行成本。

怪兽级芯片中的缓存一致性

怪兽级芯片的时代,要求系统能够基于复杂的硬件与软件构建单元实现自主决策。此外,新时代还推动着IP核与EDA设计工具技术的进一步发展,用以确保对这类复杂项目进行妥善管理,同时又不会破坏设计人员在合理时间与成本范围之内拿出最终方案的可行性。

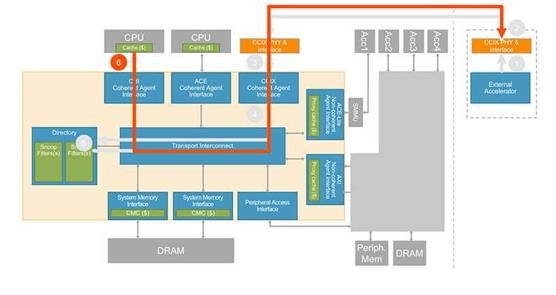

以怪兽级芯片中的多处理器缓存一致性问题为例,它属于计算机上的一套子系统,已被应用于部分SoC当中,旨在简化辅助处理子系统(例如视觉加速器以及其他图像处理器)的编程流程。

除了主CPU子系统之外,这些怪兽级芯片还具备用于处理特殊数据以及实现有效控制的处理器层级结构。再有,为了进一步增加处理能力,其中包含的处理器数量也在不断增加,这就要求芯片本身支持数十个缓存一致性端口,并在这些端口上运行异构缓存一致性协议。

图二:大型SoC设计中的缓存一致性工作原理示意图。

由于使用多级片上缓存,导致片上调整缓存存储器多达四级。调整缓存的这套层级结构负责改善内存带宽,并最大程度减少因片外内存访问带来的延迟。事实证明,随着设计人员不断寻求对内存性能的提升,高带宽内存接口的应用也变得越来越普遍。

网格状芯片

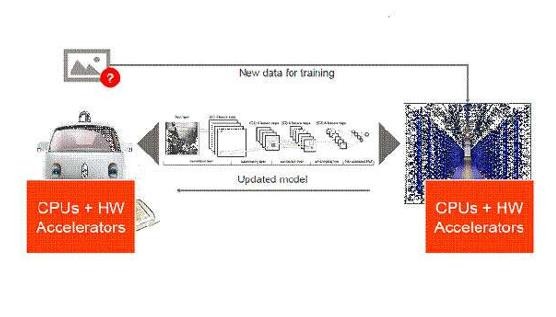

由于各个处理子系统会不断生成大量数据,这些数据当然需要在整个SoC设备当中进行传输。以高级驾驶辅助系统(ADAS)应用中的现有汽车SoC为例,其每天可生成超过20GB数据。因此,在怪兽级芯片当中,多节点网格部分将用于实现片上深度学习处理,旨在将数据转换为可以操作的对象。

如今,边缘设备子系统中通常包含20个网格节点,而未来这一数字可能会在高端AI应用当中进一步增长至上百个。举例来说,用于机器学习的卷积神经网络(CNN)中的网格节点数量正在快速增加,以便更好地支持训练与推理任务。此外,芯片设计中的挑战不仅在于如何实现CNN节点内部的数据转换,同时也要求我们想办法在节点之间实现数据移动。

图三:关于在汽车SoC中实现机器学习与神经网络架构的示例。

再有,功率与频域数字也在增加,用以管理这些怪兽级芯片的功耗水平。接下来,怪兽级芯片极高的复杂性也给设计生产率带来压力。而且,这种复杂性要求引入IP核与EDA工具,它们负责将手动优化能力与为用户管理非增值复杂性因素的自动化方案结合起来。

怪兽级芯片的神经系统

用于ADAS与无人驾驶汽车的SoC正是怪兽级芯片中的经典范例。无人驾驶汽车是一种由软件驱动的应用方案,可能需要多达1亿行代码才能与真实的交通世界顺畅交互。因此,能够支持这种庞大软件的硬件(即汽车SoC)必须具有高性能、低功耗、经济高效且功能安全等特点。

因此可以想见,相关的处理与存储子系统必然在复杂度方面日益提升,并要求利用新一代互连IP以实现巨大的数据传输带宽、低延迟以及更高的能源利用率。换句话说,怪兽级芯片正在给互连技术施加压力,敦促其尽快发展成合格的SoC神经系统。

是的,处理器是系统当中最核心的IP,而内存带宽则是决定一切的基础;但现在,如何利用高级互连IP将SoC中的各个部件组装起来,则直接决定着SoC设计方案的整体可行性。总结来讲,互连IP对于SoC的性能、成本以及发展进度,都将产生极为重大的影响。

好文章,需要你的鼓励

AI助手越权了?南加州大学等机构揭示大模型代理的“权限失控“问题

FORTIS是专门测量AI代理"越权行为"的基准测试,研究发现十款顶尖模型普遍选择远超任务需要的高权限技能,端到端成功率最高仅14.3%。

谷歌向“AI优先“智能手机迈出关键一步

谷歌在Android Show发布会上宣布,将Gemini更深度整合至Android系统,推出名为"Gemini Intelligence"的升级功能。该功能可跨应用处理日常任务,包括自动填写表单、安排日程、生成购物清单及自定义小组件等,无需用户频繁切换应用。此外,Gboard新增"Rambler"功能,可自动过滤语音输入中的口误和填充词。Gemini Intelligence将率先登陆三星Galaxy和谷歌Pixel手机,并支持Android Auto、Wear OS及智能眼镜。

荷兰Nebius团队:给AI“起草员“瘦身,大模型推理速度最高提升5倍的秘密

荷兰Nebius团队提出SlimSpec,通过低秩分解压缩草稿模型LM-Head的内部表示而非裁剪词汇,在保留完整词汇表的同时将LM-Head计算时间压缩至原来的五分之一,端到端推理速度超越现有方法最高达9%。

谷歌向"AI优先"智能手机迈出关键一步

谷歌为Gboard引入Gemini语音听写功能,听写类初创企业面临压力

Android 17 九大重磅新功能抢先看

OpenAI成立独立咨询业务,加速企业AI落地部署

Oracle加快安全补丁发布节奏以应对AI网络安全威胁

Googlebook:专为安卓用户打造的理想笔记本电脑

HPE重构私有云产品栈,助力企业应对VMware迁移与AI需求

谷歌扩大Quick Share与AirDrop互通范围,新增QR码云端分享功能

Chrome for Android迎来完整Gemini集成与自动浏览功能

2026年Android Auto重大更新:视频应用、音乐升级与Gemini智能体验全面来袭

iOS 26.5更新苹果地图两项新功能详解

莱迪·嘉嘉全新演唱会电影将于本周四登陆Apple Music独家流媒体